Dear all,

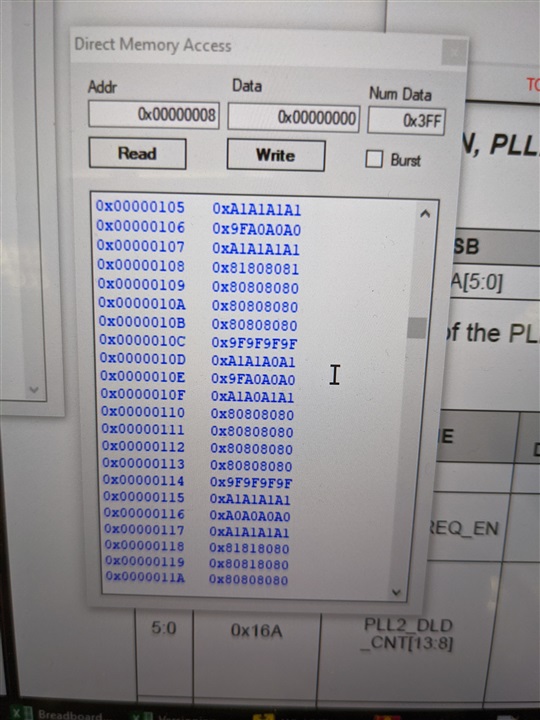

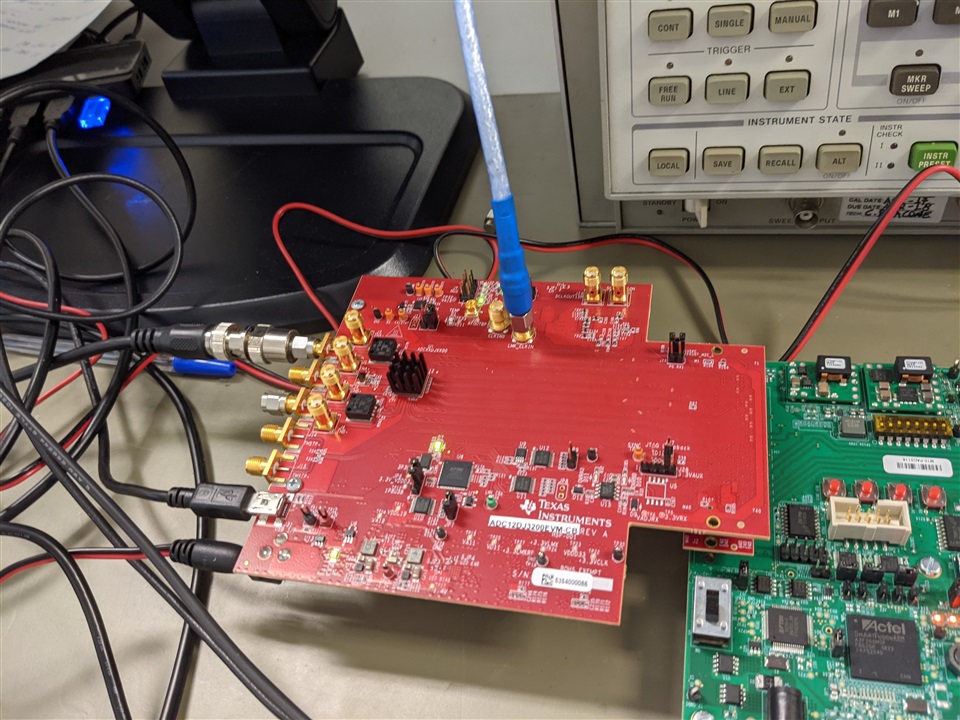

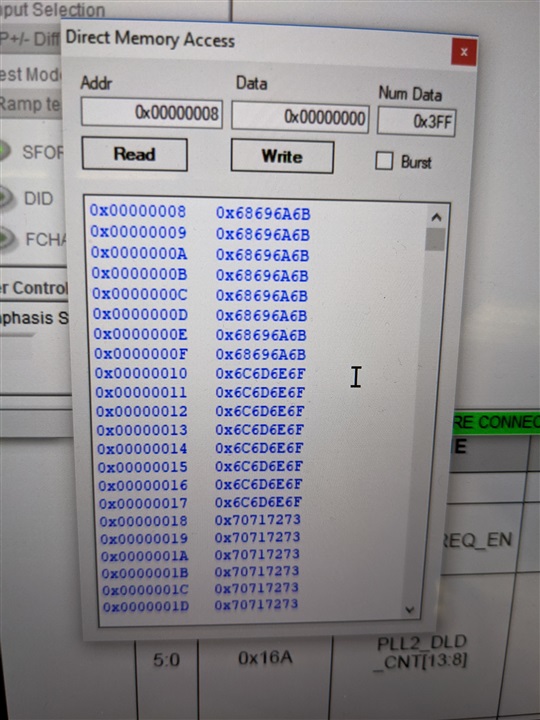

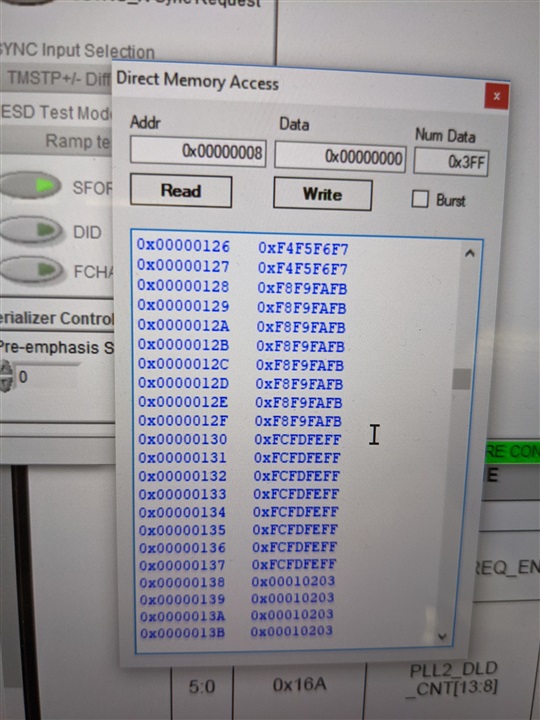

we have a problem aligning the lanes in JESD204B IF. We use JMODE7 in the ADC12DJ3200 EVM with 8 lanes (2 channels, 8 bit per ch). When we run the ramp test, we see the lanes aligned but not in the operative mode, when sampling an analogue sine wave. We use K=32 and we interface with the Microsemi JESD RX Macro running in the PolarFire EVM connected by FMC connector. We use direct external clocking at 1440 MHz (SysRef = 2.8125 MHz).

Any clue ? Thank you very much,

Valerio