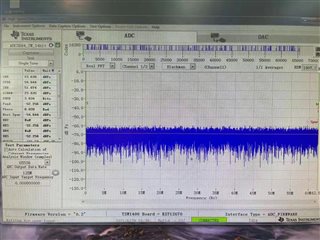

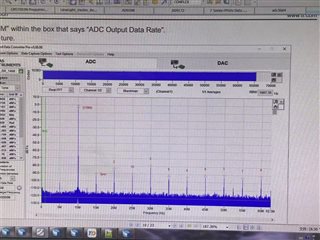

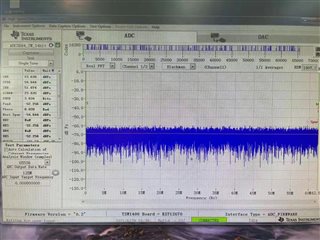

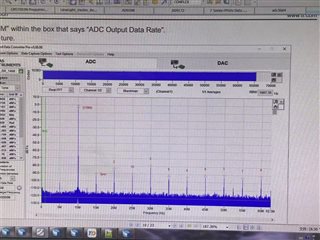

Hello, the customer feedback that after the arrival of this part, the spectrum bottom noise test value is more than -50, which does not meet the specifications.

Please help to implement the situation, thank you.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello, the customer feedback that after the arrival of this part, the spectrum bottom noise test value is more than -50, which does not meet the specifications.

Please help to implement the situation, thank you.

Hi Allison,

Please have the customer ensure that the sample clock (125 MHz) and DCLKIN (437.5 MHz) are sharing a reference frequency (usually 10 MHz). If this is not done, bit errors may occur.

Is the customer observing the high noise floor on CHB? This can be observed by selecting "Channel 2/2" on the HSDC Pro screen.

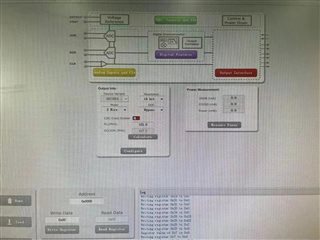

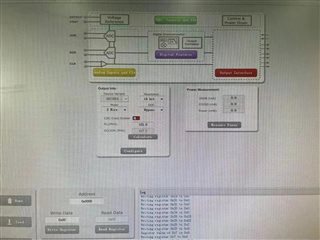

Please have the customer enable the Ramp Pattern test mode. The instruction for this are located on page 21 of the ADC3664EVM User's Guide. The ramp should appear as shown in the guide. Please have the customer share an image of the ramp from their setup.

Best Regards,

Dan