Other Parts Discussed in Thread: ADC12QJ1600

Hi, experts,

I'm assessing the ADC12xJ1600 for our LiDAR project, now I have 2 issues, could you please help me check in details? thanks a lot.

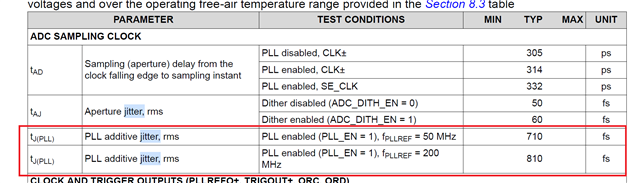

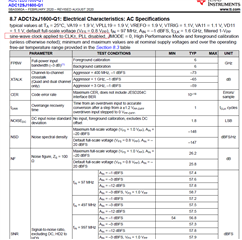

1. internal CPLL output jitter: from the d/s, the PLL additive jitter is >700ps. But for the 12bits ADC@1GSPS, my understanding is that the sample clock jitter should be <200fs to get the expected SNR performance. could you please help me confirm again if this internal CPLL can be used for this application? Also could you please help provide the detailed clock jitter or phase nosie requried for 12bits@1GSPS applicaiton case? it is appreciated if you can help provide the clock design solution here. thanks.

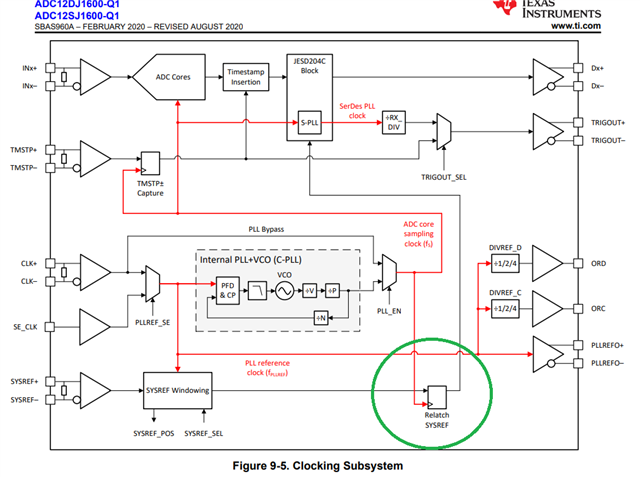

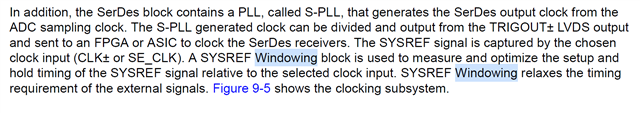

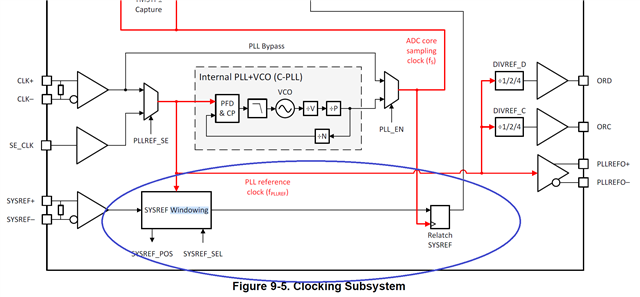

2. regarding the SYNREF, how to undestand the descriptions in d/s? could you please help give me one example to use SYSREF here? based on my understanding, the sync. clock from "SYSREF Windowing" block is relatched by the ADC core sampling clock, also since the PLL refer clock phase is NOT aligned with the internal PLL output, so it sounds the SYSREF windowing block doesn't work if itnernal CPLL is enabled, correct?

best regards,

Feng

SNR is measured when CPLL disabled. can you plesae help share the SNR/SINAD test data when CPLL is enabled in ADC12QJ1600 EVM board? thank a lot.

SNR is measured when CPLL disabled. can you plesae help share the SNR/SINAD test data when CPLL is enabled in ADC12QJ1600 EVM board? thank a lot.