Other Parts Discussed in Thread: LMK04832, , LMK04828

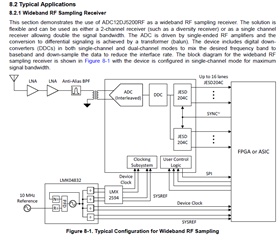

In the ADC12DJ5200RF datasheet section 8.2: Typical Applications, figure 8-1, a Wideband RF sampling Receiver block diagram is shown with the SYSREF signal being generated by the LMK04832 synthesizer to the FPGA and the ADC.

My question is, isn't it better for the FPGA to generate the SYSREF signal? Since the FPGA is the device that controls the timing of all devices on the board, which can include multiple ADCs and DACs, isn't it more straight forward to have the FPGA to generate and control the SYSREF signal? What are the trade-offs?

Thank you.