Other Parts Discussed in Thread: DAC38J84

Hi,

I am using the DAC38J84 on the EVM with an Arria10 dev board and for now, the JESD part works fine. However I am facing a problem using the NCO on this DAC. For my project, I plan to use the NCO to shift the input frequencies to higher ones and I need to really control the phase of the NCO output, that is I need to have a constant time between the NCO reset assertion and the NCO output phase reset with the device clock and interpolation used.

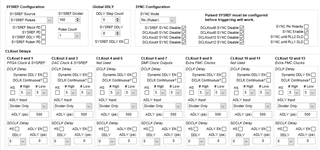

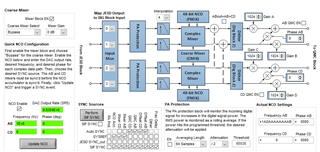

To do that, I use the SYSREF sync source on the Mixer AB, Mixer CD and NCO Acc. Here are the steps to achieve the test that I am doing :

- Program the FPGA with an image containing a JESD204b TX.

- Establish the JESD link between the EVM and FPGA.

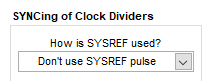

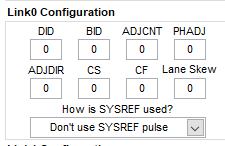

- Once the link has been established, disable the SYSREF syncing to the clock dividers and the and to the JESD link0

- Change the pulser to be only 1 pulse

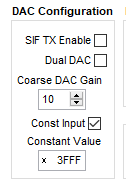

- Use the constant input to the dac option

- Configure the NCO

- create a SYSREF pulse by using the Sysref trigger button on the EVM.

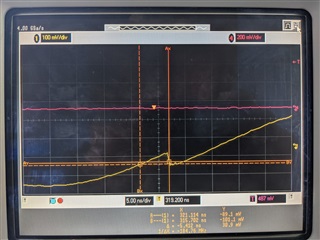

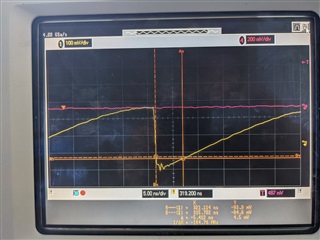

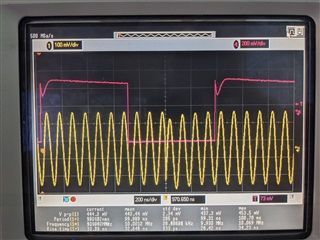

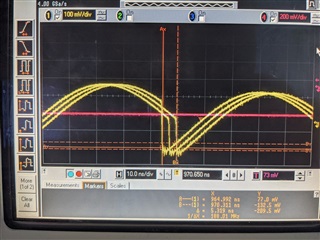

- Use the falling edge of the SYSREF pulse as trigger and capture the DAC A output.

- Monitor the time between the falling edge trig point and the point of phase disruption of the output sine.

Doing this, the time seems to vary quite a lot (up to 10ns). Is this something expected from the EVM? Is this due to the AC coupling of the SYSREF on the eval board? Is there a way to have a constant time between sysref and nco phase output reset?

Thanks!