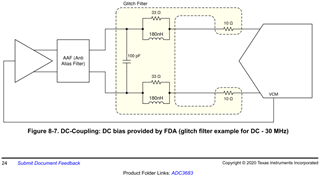

I do not really understand the function / the effect of the recommended Glitch Filter between AAF and ADC. The description in the ADC data sheet is not detailed enough for me. The EVM uses different values for the Glitch Filter than the ADC data sheet.

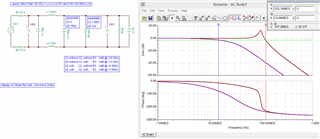

However, I have to design an AAF stage together with the Glitch Filter suitable to our requirements. The AC Transfer characteristic with that Glitch Filter design strongly depends from the input impedance of the ADC input.

Is there any description how to calculate the values for R, L and C’s of the Glitch Filter?

Is it sufficient, to use the ADC data sheet input impedance values 8kOhm and 7pF for the AC simulation of the filters?

Or depends the ADC input impedance from the sampling frequency?

Our requirements are: sampling frequency 62.5MHz, used analog bandwidth DC to 15MHz, Antialiasing & Glitch Filter Low pass cutoff at 15MHz (-3dB), stopband from 60MHz (<-50dB)

Thanks in advance.