Other Parts Discussed in Thread: OPA2387, ADS127L01

Hi,

I have following three questions regarding the ADC Chip ADS1278.

1. As shown in the following picture, I want to see if my approach will work. I am converting a differential signal into single mode signal of 1V and injecting into the ADC ADS1278. The Signal can not go negative because the OPAM OPA2387 is single side biased. I want to confirm if this approach will work ?

2. The ADC will be interfaced with TIVA TM4C129 SPI port, Can I use the Syn Pin to hold the ADC and release for start of conversion when required ? If not how can I keep the ADC on hold and then start a conversion ?

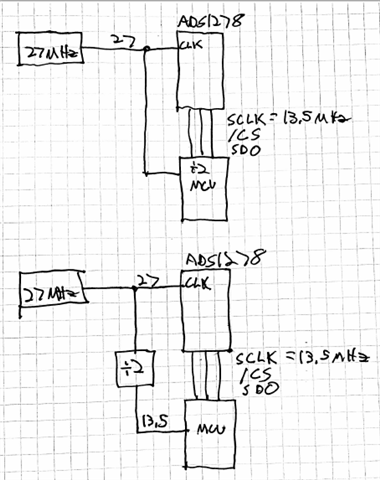

3. The SPI will be communicating at 10MHz Clock supplied by the controller to the ADC on Pin SCLK while the ADC be connected to a free running 27MHz Crystal via J9 connector. The ADC will be in High Resolution Mode. Will it work this way in High Resolution mode?

Thanks