Other Parts Discussed in Thread: ADS54J40

Hello,

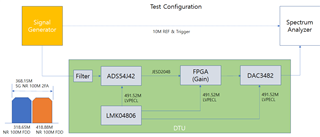

My customer tested the error vector magnitude(EVM) of a 5G NR signal with the following configuration.

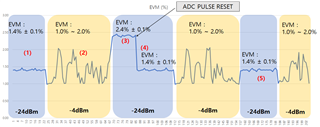

The result of measuring EVM while changing the SG's 5G NR signal power to -24dBm and -4dBm two cases is as follows.

(1) It shows stable EVM characteristics for -24dBm input.

(2) When changing to -4dBm, the EVM deviation increases to about 1% and is unstable.

(3) If you change the input to -24dBm when the EVM value is bad, the EVM deviation will be stabilized, but the EVM value will remain bad.

(4) Running a PULSE RESET of the ADS54J42 makes the EVM values good again.

(5) If changing the input from -4dBm input to -24dBm at the moment when EVM value is good, both EVM deviation and EVM value are normal.

Please advise on the causes and solutions of the above abnormal symptoms.

Thanks a lot.

JH