I’m attempting to get the DAC3482 running on a custom board. It seems like most things are “working”, but the generated output is scrambled. To make sure the register settings were OK, I was able to test them on the DAC3482 Eval board. Using this reg configuration, everything worked fine on the eval board and it generated the expected output. The differences between the eval board and my custom board are minor, such as the custom board has no OSTR or SYNC clocks. But I disable these signals, so they should not matter.

First some background info:

- Interpolation mode = 8x

- Syncing Mode = Single Sync Source (using FRAME)

Signals

- Data Clock = 150 MHz

- DAC Clock = 150 MHz

- Frame Clock = 150/16. Pulse high = 13.3 ns, Pulse period = 106 ns.

The data and dac clocks are the same freq and locked. There is a phase delay of ~2 ns between them.

The PLL is enabled and being used to multiple the 150 MHz data clock (8x) to FDac = 1.2 GHz.

PLL setting:

- M = 8

- Prescalar = 3

- N = 1

- Freq PFD = 150 MHz

- DAC clock = (150*8) = 1.2 GHz

- Fvco = 3600 MHz

- vcoitune = 1

- pll_vco = 32

- Charge pump = Single

The PLL alarm bit is clear.

The fine mixer is being used and mixing the input stream by 200 MHz. For this test, the data is a simple IQ sine wave at 1 MHz.

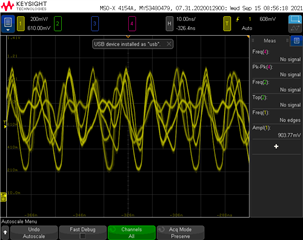

Unfortunately, the output on my custom board is kind of a mess.

Some more info:

Data capture

I have scope captures that shows good clocks with solid setup and hold times for the data. At 150 MHz, it’s not too difficult. But I don’t believe data capture is an issue, as we have been able to implement the IOTest pattern generator in the FPGA driving the DAC. We get no IOTest or Parity errors (After adjusting the delays). Also, a Sanity check passes (ie. you turn off the Pattern generator, error re-appear). This would indicate we have good data capture.

FIFO errors

As above, we have no FIFO errors/alarms. So I don’t believe hand-off from the DATA to DAC domain is an problem.

Output Drive

The direct DAC generation feature can be used and it works as expected. If we directly drive the DAC, output changes as expected.

Suggestions would be appreciated….