Other Parts Discussed in Thread: ADS124S08

Hi,

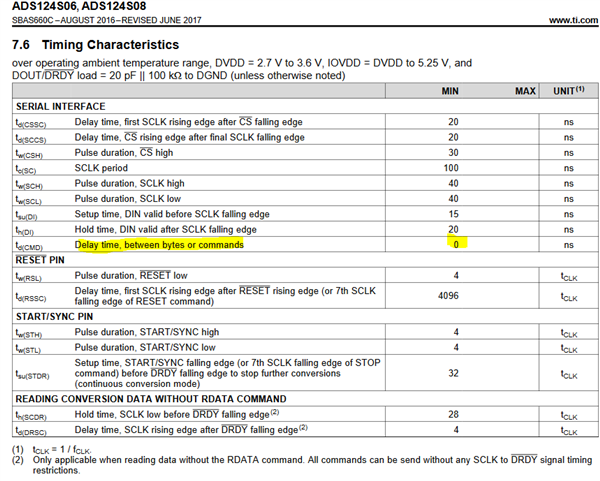

I just would to know what would be the equivalent of timing t11 : Final SCLK falling edge of command to first SCLK rising edge of next command (ADS1256)

on the ADS124S08 ?

From my reading of the spec ADS124S08 ... this would be th(SCDR) = 28 tclk on Figure 6 - Page 16

Is my assumption correct ? Thank you in advance