Other Parts Discussed in Thread: LAUNCHXL-F28379D, , ADS7038

Hello,

We bought the ADS7038Q1EVM-PDK evaluation board. I removed the daughter-board containing the ADC IC from the PAMboard and connected it directly to my LAUNCHXL-F28379D board.

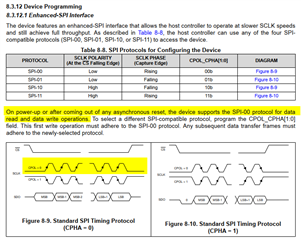

My LP program is ostensibly talking to the ADC at 500kbps using SPIB and I am able to get plausible samples on AIN0. However, I’m nervous the clocking scheme only works marginally and won’t be robust at full speed so I want to be sure the F2837xD (Master) clocking scheme is the correct one on paper too.

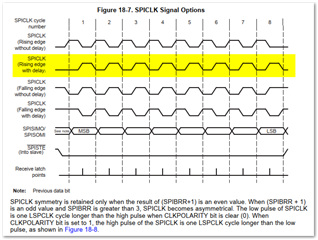

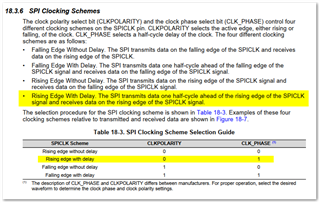

The default clocking scheme of the ADS7038 (Slave) is SPI-00 (CPOL = 0 and CPHA = 0). After comparing the timing diagrams of the ADC and microcontroller, I conclude that the correct clocking scheme in the F2837xD is “Rising Edge With Delay” (POL = 0, PHA = 1), is that correct please?

ADS7038:

F2837xD Manual:

Thank you very much.