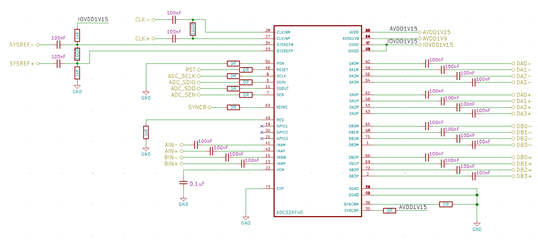

I am using ADC32RF45 on a board of my own design. I would like to use the single ended SYNCB signal to pin 63.

When I write Jesd Digital page register 6036h to the value 40h to assert the CMOS SYNCB setting, then I can no longer complete SPI reads from the ADC. I have probed the SDOUT pin and observed no activity. When I set that register back to 0h, SDOUT starts working again.

I do not observe this behaviour when I set that bit high for register 7036h.

What could be causing this problem?