Hi,

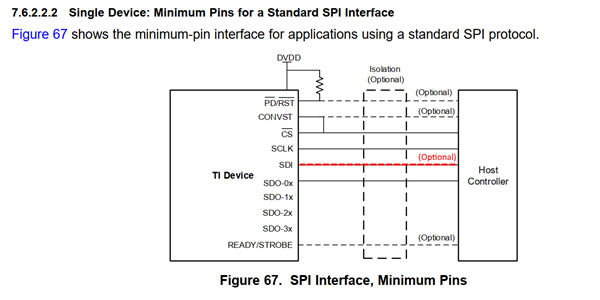

I have a question about the pin configuration where nCS is tied to CONVST as shown in Figure 67 on p. 40 of the datasheet.

How is the device configuration handled in this case because it's not possible to keep CONVST high during register write or read?

There is a note in the datasheet (7.6.3) that the host must keep CONVST high for reading and writing the registers. This is not possible due to the connection to nCS.

How should the SPI communication look like in this case?

Best regards,

Alex