Hi sir,

Do you have any recommendation for biasing the TMSTP+ signal on ADC12DJ5200RF?

Non-differential setting.

Also the Which Voltage should it be biased with if any specific is required?

Thanks.

Regards,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi sir,

Do you have any recommendation for biasing the TMSTP+ signal on ADC12DJ5200RF?

Non-differential setting.

Also the Which Voltage should it be biased with if any specific is required?

Thanks.

Regards,

Hi Frank1,

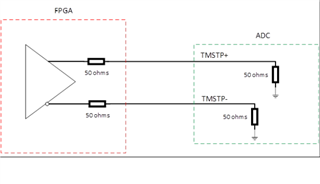

I would recommend to either use the 1.8V HSTL or SSTL standard IO on the FPGA. Generally the FPGA has internal series 50ohms resistors and the ADC also has 50 Ohms to ground for each leg when TMSTP_LVPECL_EN = 1. So in theory the circuit shown below should work and there shouldn’t be a need to add any component . If the FPGA does not have the Series 50ohms inside the FPGA you can add them on the board on each line.

Regards,

Neeraj

Hi Neeraj,

Thank you for your response.

Well our implementation is a little different.

We have an original design that we would like to change.

The input is a single eded analog signal from an RFoF and AC coupled. Which means that we only get a pulse on the input.

And in datasheet is states that the inputs (TMSTP) must be externally biased.

Any recommendations on the biasing?

Thanks.

Hi Frank1,

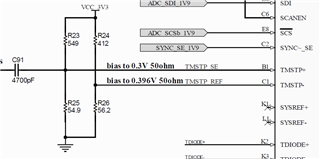

They way you have biased TMSTP looks ok to me. Do you want to the signal on TMSTP pins to differential or just single ended?

Regards,

Neeraj

Hi Neeraj,

1) We would like to bias using 1.1V or 1.9V instead since 3.3V carry noise into the ADC.

2) The input signal is just a single ended pulse (1PPS) which means that when the pulse dies out (due to AC coupling) the inputs to the ADC will only see the difference in bias (0.096V) which is less that the specified 0.4V diff requirement for the ADC.

Will this work then?

Thank you.

Hi Frank1,

Yes, you can bias using 1.1V or 1.9V.

Yes, I think you proposal should work.

Regards,

Neeraj

Hi Neeraj,

Does this mean that for the ADC to detect a "0" on TMSTP it only require -0.096V between + and -?

Why is it then specified 0.4V in data sheet?

Is there a hysteresis on the inputs?

Thanks.

Hi Frank1,

If the differential voltage is below 0.4V the input will register it as a "0'. if it more than that it will register it as "1".

Regards,

Neeraj

Hi Neeraj,

customer wanna to confirm the following to ensure his understand correctly.

Please forgive me for asking more questions about this, but I must be sure that I understand you correctly.

What you say is that if TMSTP+ is 0.4V higher than TMSTP- it will be register a "1".

And if TMSTP+ is 0.3V higher than TMSTP- it will register a "0". Also if the difference ("TMSTP+" - "TMSTP-") is 0V or even -0.4V it will register a "0".

Is this correct?

Thanks.

Hi Frank1,

Signal seen by differential TMSTP input is TMSTP - (TMSTP-). Hence the result should always be positive differential voltage.

Regards,

Neeraj

Hi Neeraj,

Are you really sure about that? That is indeed a strange differential receiver in that case.

A differential voltage is both positive and negative.

BR

Magnus