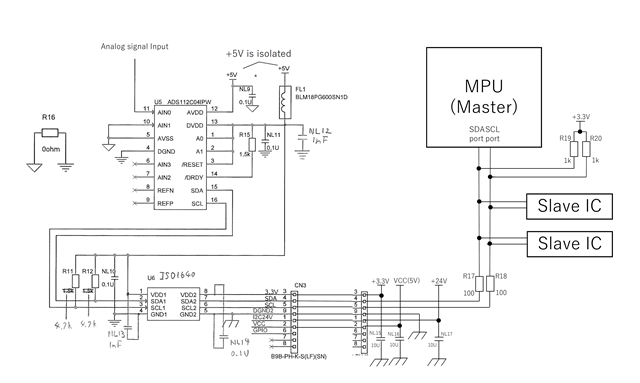

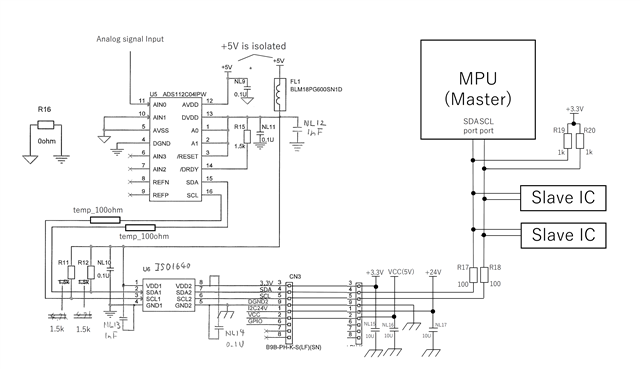

Other Parts Discussed in Thread: ISO1640, ADS1119, ADS122C04EVM

Hi team,

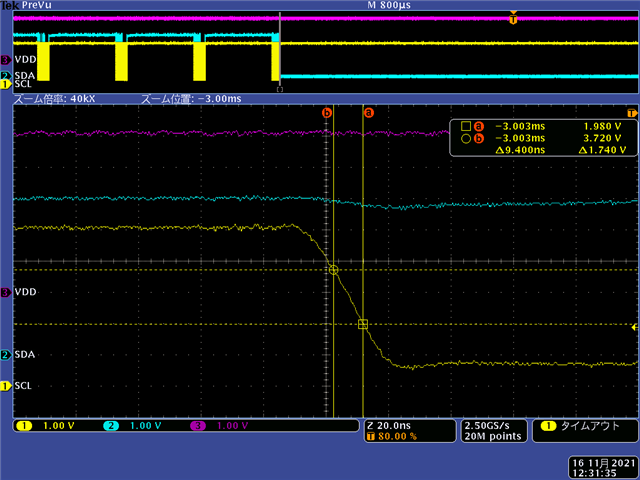

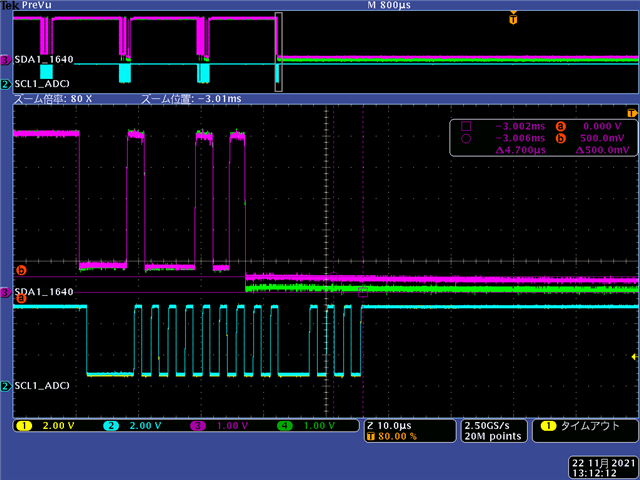

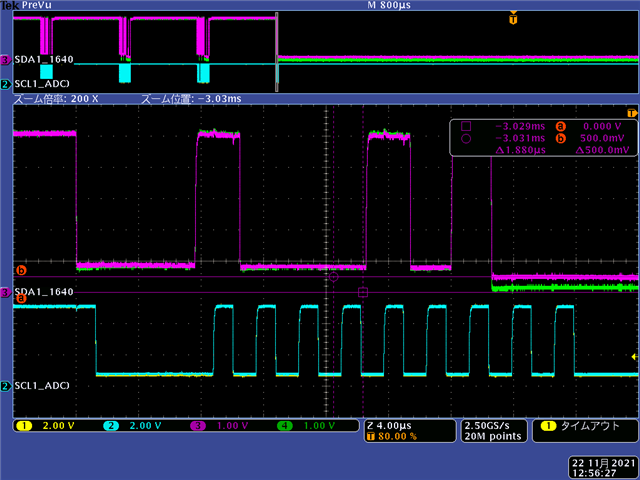

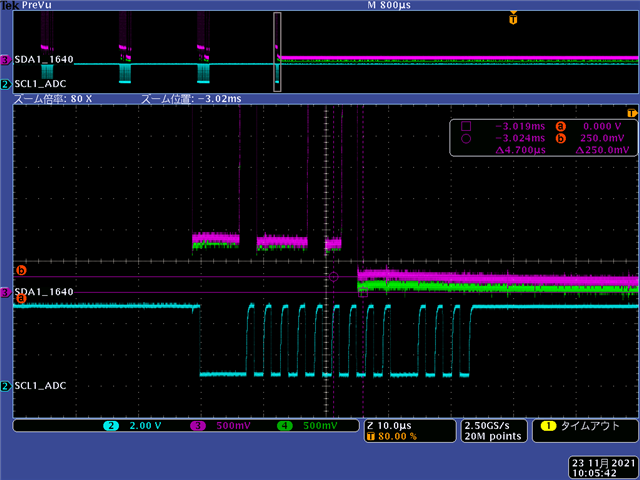

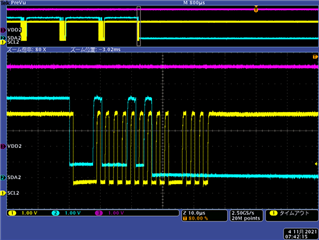

ADS112C04 keeps the SDA signal Low.

Why does this happen?

Purple: DVDD

Yellow :SCL

Blue :SDA

There is ISO1640 between MCU and ADS112C04 and GND of MCU side is rising.

Sincerely.

Kengo.