Other Parts Discussed in Thread: LMK04828

Hi team

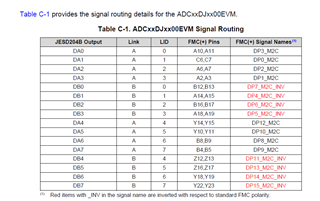

I am using internal ramp pattern to check whether it is properly been received at the FPGA side. I am using JMODE 2, with Fs=1250 MSPS. The Serdes is operated at 5Gbps.

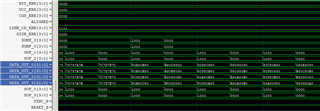

As per the data sheet, "In the ramp test mode, the JESD204B link layer operates normally, but the transport layer is disabled and the

input from the formatter is ignored. After the ILA sequence, each lane transmits an identical octet stream that

increments from 0x00 to 0xFF and repeats". But i see the below patterns at my end which dont look like identical with incrementing patterms.

While programming the ADC card, SYNC status=1, JESD LINK=1 while reading register at address 208. Also VALID signal related to transceivers lanes (at FPGA side) is 1 which indicates that recovered data is valid.

Any idea what is happening here?

Regards

Rohit