Hello,

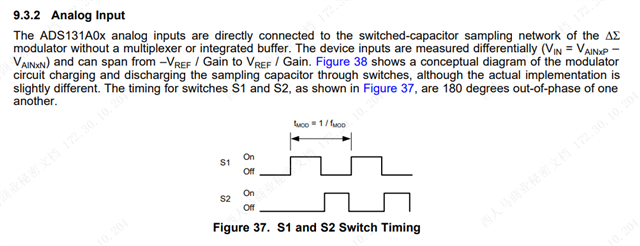

The sample holder sampled at a frequency of fMOD (4.096 MHz), which means the sampling time is only T_mod/2 (approximately 0.122uS), as described in ADS131A04 Manual 9.3.2 (as shown in the figure below). If the sampling capacitance is 24 bits accurate during this time, the output impedance of the input is small to meet the requirement.

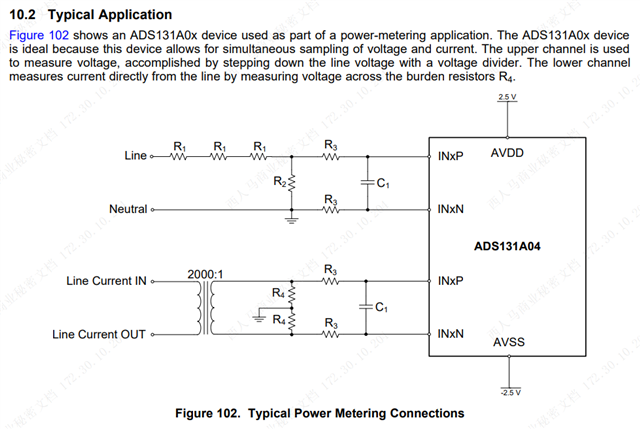

However, in accordance with the typical application 10.2 in the manual (shown below), where R3=100Ω and C1=2.7nF, as input RC, should not achieve a sampling capacitance of 24bit (or even 20bit) accuracy over the time of T_mod/2. The training:

https://training.ti.com/ti-precision-labs-adcs-introduction-sar-adc-front-end-component-selection

Is there a misunderstanding about the sample retention process or sample time for the ADS131A04?

Best regards

Kailyn