Hello E2E,

What is the assumption that the voltage of the sampling clock signal (FPGA_CLK signal input from the H4 pin of the FMC connector) input via the FMC connector is designed?

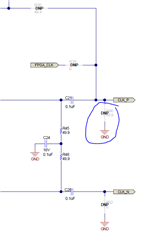

If you input a 2.5V single-ended clock with reference to VADJ-2.5V in the circuit diagram, it will exceed the rated voltage (2.1V) of the AD converter.

Since the level shifter is placed, it seems that the SPI signal etc. can input 2.5V, but the sampling clock seems to be directly connected to the AD converter. Is it okay to think that inputting as a 1.8V single-ended signal is the correct usage?

Regards,

ACGUY