Other Parts Discussed in Thread: DAC38J84

DEAR TI,

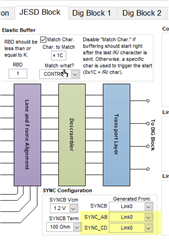

I am using a third party alinx xczu9eg ultrascale+mpsoc development board for JESD204B based DA development(DAC38J84EVM), The FMC daughter board I am using is DAC38J84EVM , where the synchronization signal SYNCBP/N of the DAC chip is connected to the F10,F11 interface of the FMC while other sync,SYNCAB,SYNCCB is also at the F row.

The critical problem is, i found the f row of my third party FPGA evaluation board is grounded!

Is there any way that I can overcome this?

best regards.

Shuai