Other Parts Discussed in Thread: ADS7038Q1EVM-PDK

Hi,

I attempt to control ADS7028 via TMS320C2000 Experiment Kit(Piccolo F28069).

My final purpose is get 2 RMS value and 2 ZCD signal from 2 Sine wave signal input. (Is this achievable?)

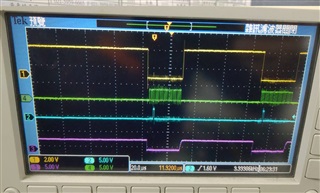

So far I have successfully send 24bit SPI frame from Experiment Kit.

Then, I tried to test read and write command of ADS7028, but it seems not respond at all.

(Write test: Set all channel to GPIO output and set logic 1 , Read test: read several registers ).

Is there any setting of SPI or my process is wrong?

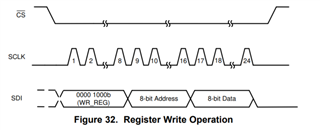

_interrupt void cpu_timer1_isr(void){ // 100us loop

if(SPI_STATE==0){

SpiaRegs.SPITXBUF=0x1000;

SpiaRegs.SPITXBUF=0x2100;

SpiaRegs.SPITXBUF=0x0000;

SPI_STATE=1;

}else if(SPI_STATE==1){

SpiaRegs.SPITXBUF=0x1000;

SpiaRegs.SPITXBUF=0x2100;

SpiaRegs.SPITXBUF=0x0000;

SPI_STATE=0;

}

if(SpiaRegs.SPIFFRX.bit.RXFFST!=0) Result= SpiaRegs.SPIRXBUF;

}

void SPI_Init(){

SpiaRegs.SPICCR.all =0x07; // 8-bit char bits

SpiaRegs.SPICTL.all =0x06; // Enable master mode, normal phase, enable talk, and SPI int disabled.

SpiaRegs.SPIBRR = 0x0016; // BAUD= LSPCLK/(SPIBRR+1)= SPIBRR=(LSPCLK/BAUD)-1

SpiaRegs.SPICCR.all =0x87; // Relinquish SPI from Reset

SpiaRegs.SPIPRI.bit.FREE = 1; // Set so breakpoints don't disturb xmission

}

void SPI_FIFO_Init(){

SpiaRegs.SPIFFTX.all=0xE040;

SpiaRegs.SPIFFRX.all=0x2044;

SpiaRegs.SPIFFCT.all=0x0;

SpiaRegs.SPITXBUF=0x0800;

SpiaRegs.SPITXBUF=0x0500;

SpiaRegs.SPITXBUF=0xFF00;

while(Inter<1000000)Inter++;

Inter=0;

SpiaRegs.SPITXBUF=0x0800;

SpiaRegs.SPITXBUF=0x0700;

SpiaRegs.SPITXBUF=0xFF00;

while(Inter<1000000)Inter++;

Inter=0;

SpiaRegs.SPITXBUF=0x0800;

SpiaRegs.SPITXBUF=0x0900;

SpiaRegs.SPITXBUF=0xFF00;

while(Inter<1000000)Inter++;

Inter=0;

SpiaRegs.SPITXBUF=0x0800;

SpiaRegs.SPITXBUF=0x0B00;

SpiaRegs.SPITXBUF=0xFF00;

while(Inter<1000000)Inter++;

Inter=0;

}

i

i