Hi everyone,

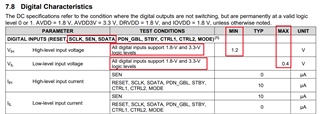

I have a question about the SPI control signals' logic level of ADS42JB46,

1) I see that this AD part can support both 1.8V and 3.3V, so how can I choose the logic level as 1.8V or 3.3V?

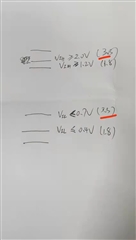

2) what's more, I don't know why in datasheet, it shows 1.8V logic level only, because as I know, the 3.3V logic level is: Vil <= 0.7V, and Vih >= 2.0V.

Best Regards,

Nan