Other Parts Discussed in Thread: TI-JESD204-IP, LMK04828

Dear Ti.

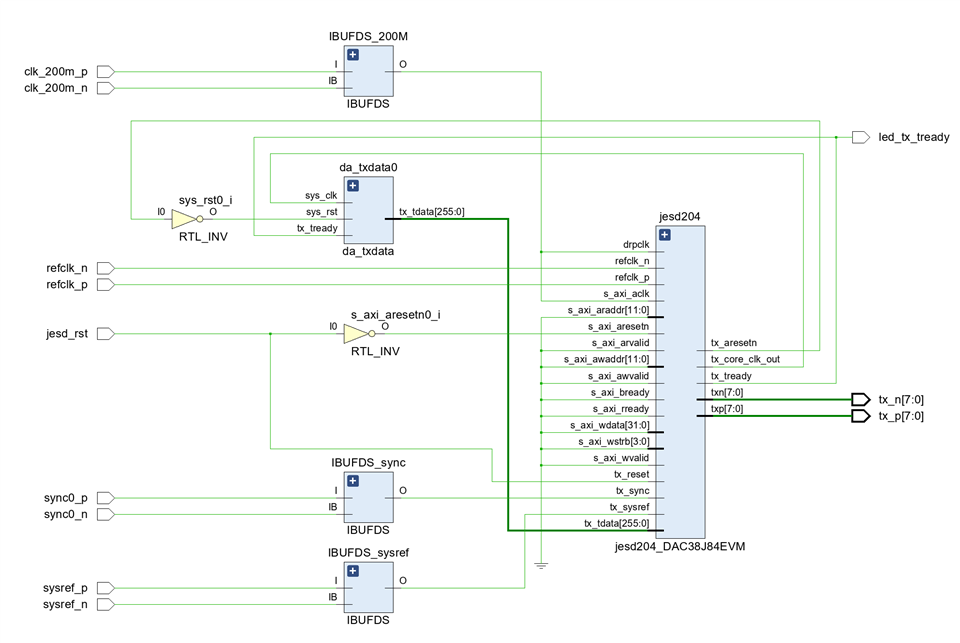

I'm using xilinx FPGA kcu040 kintex ultrascale trying to drive the DAC38J84EVM, all pins should have been assigned properly.

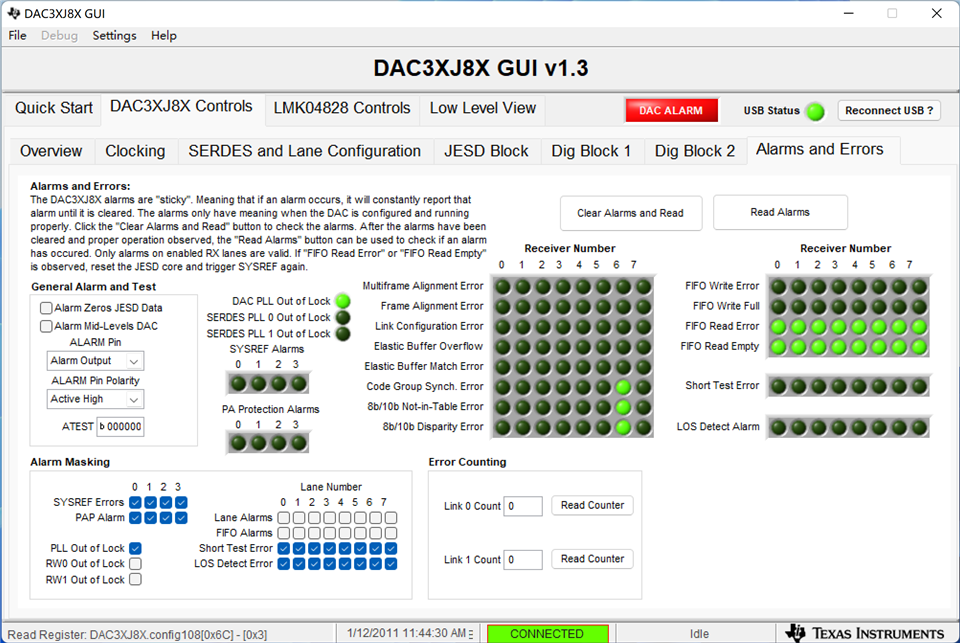

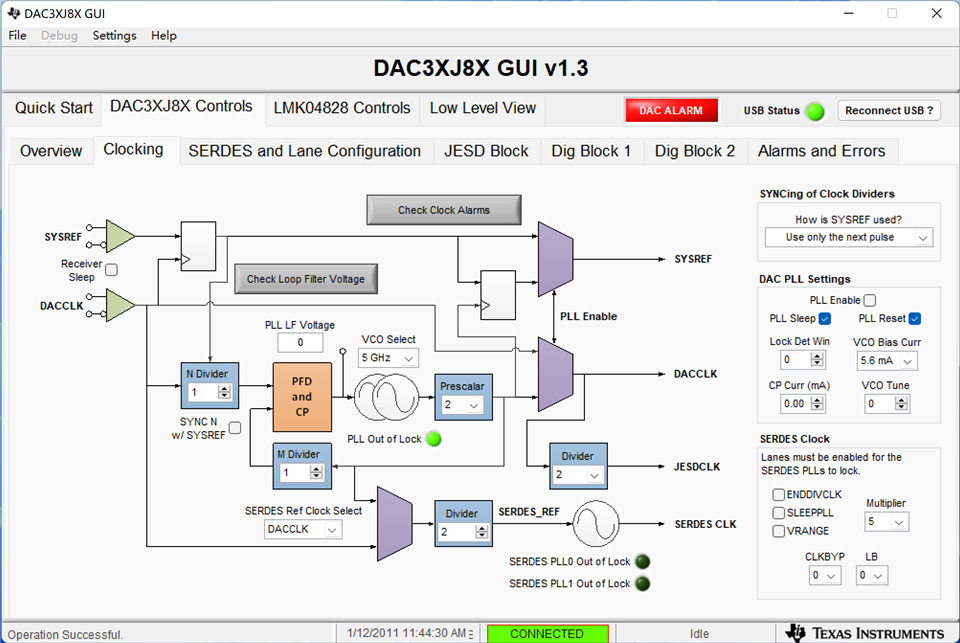

I have tried both TI-JESD204-IP and XILINX JESD204 IP.(When I'm using TI-JESD204-IP, I blocked the adc out put and adc input).Both design finally came out with the same "DAC alarm" ---DAC PLL OUT of LOCK.

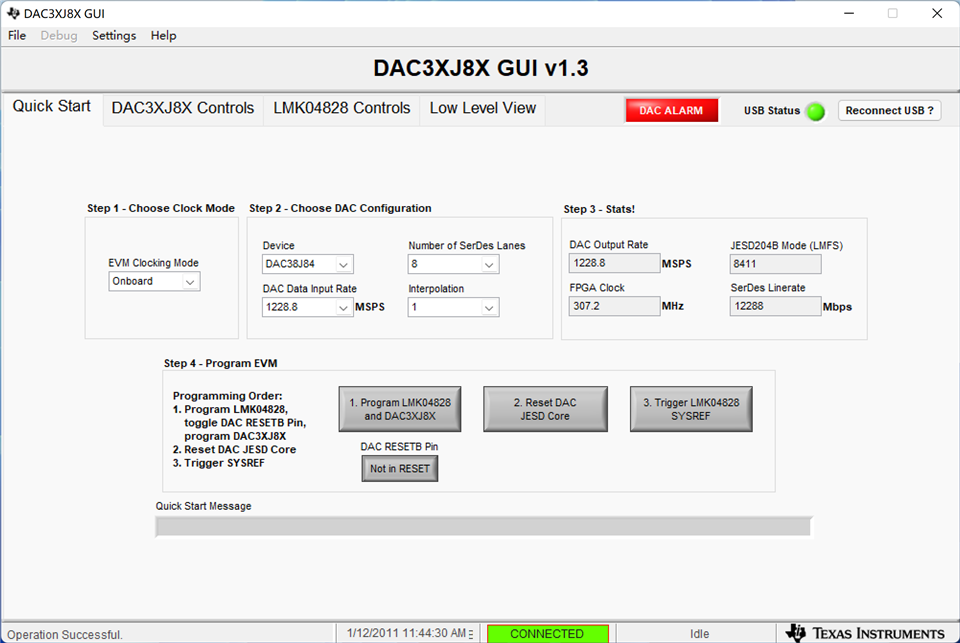

My configuration is:

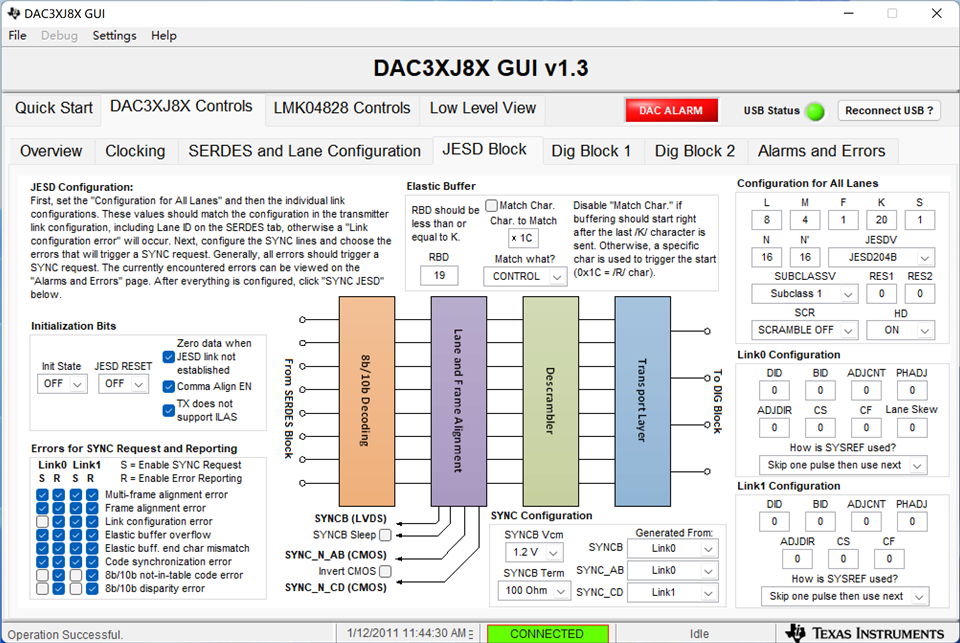

LMFS: 8411

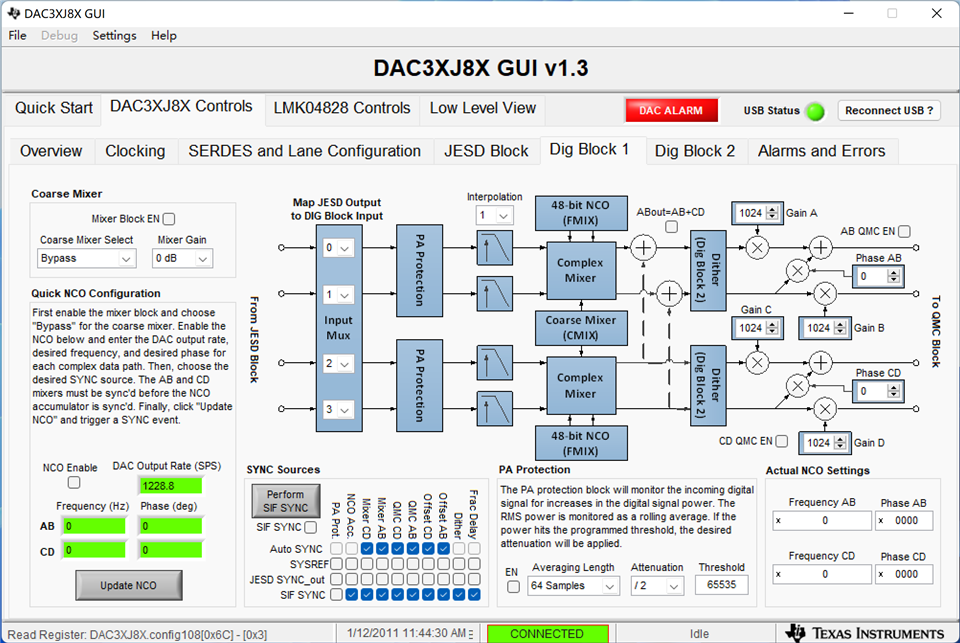

sample rate: 1228.8MSPS,

interpolation: 1

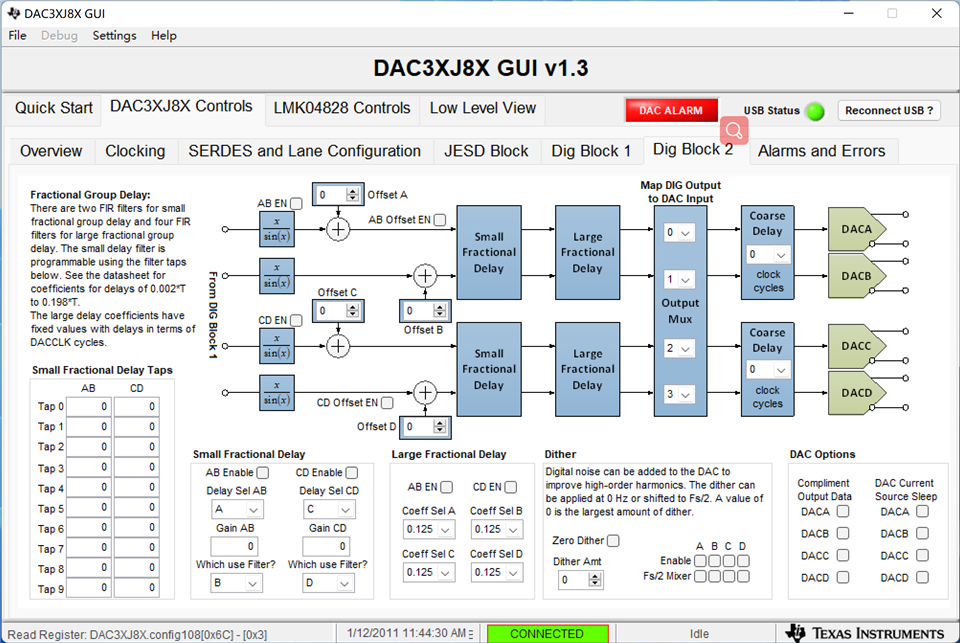

Other detailed settings are automatically generated by the Quick start page following the DAC3XJ8XEVM guide book's chapter 4.3 'DAC3XJ8X Quick-Start Procedure'.

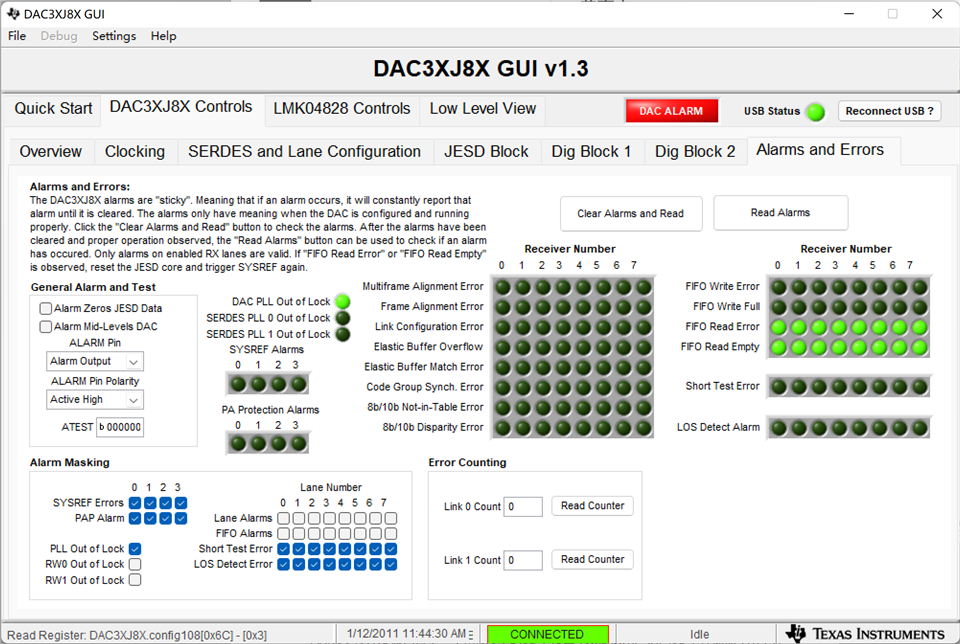

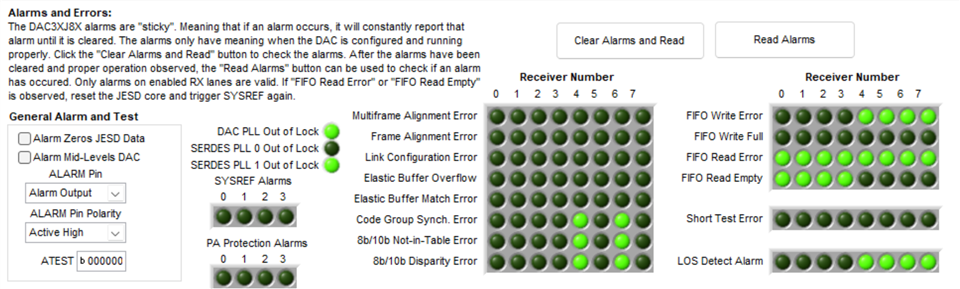

The ALARM and Errors page:

Here is my cfg from 'Low Level View' Page:cfg.cfg.

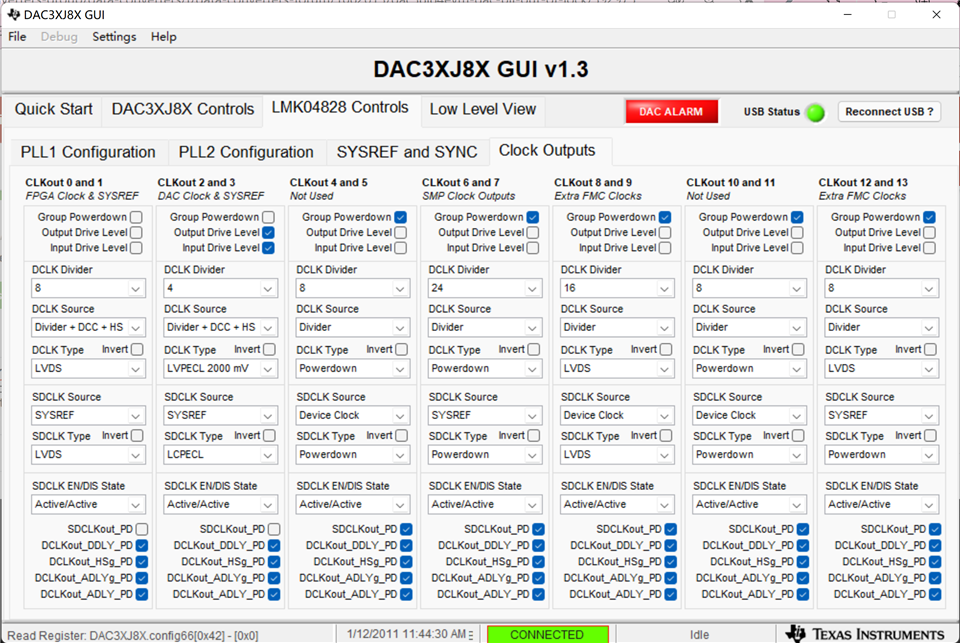

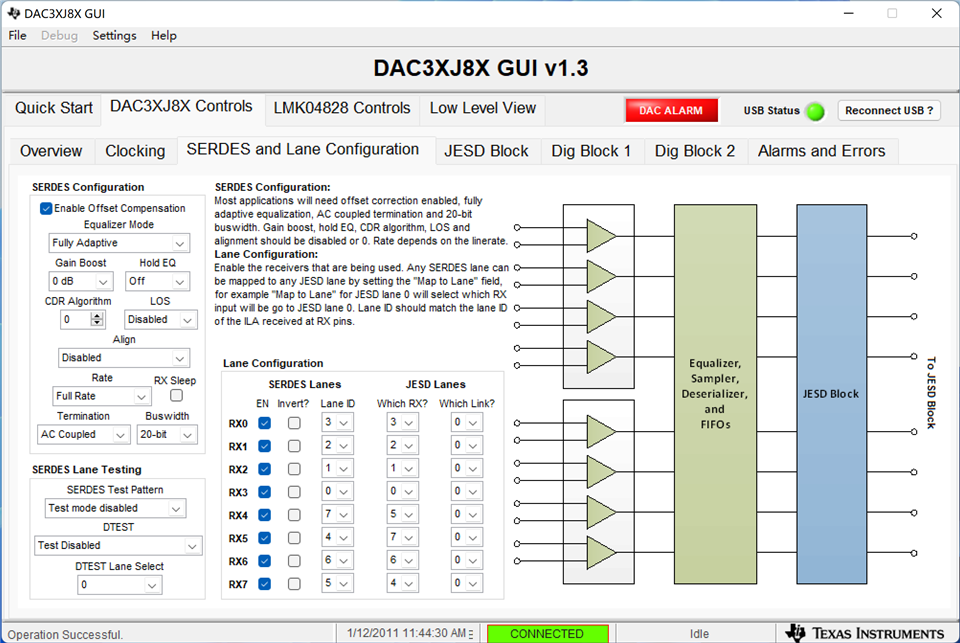

some detailed settings:

I have searched some posts in the forum, but their configuration is not quite the same as mine. I tried to follow some posts, but failed.It seems I have to set pll_vcosel,pll_vco...But I didn't find where and how to set there parameters correctly

Please help me to config the settings.