Hello;

We got a PCN from TI (Notification# 20211209001) which states that the Daisy-chain operation is deleted out of the datasheet of the DAC7750.

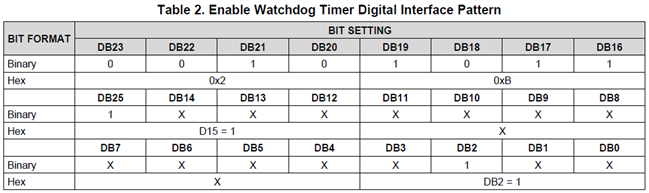

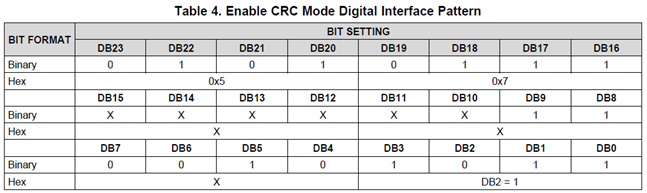

In the E2E threads we found that problems occur in daisy-chain operation with watchdog-timer and frame error checking.

We already use the DAC7750 in daisy-chain operation (3 devices), no other SPI devices and ignore the alarm's.

We didn't find errors so far for several years

Is it safe to keep using it this way?

With kind regards;

Pieter Simons