Other Parts Discussed in Thread: AFE58JD28

Dear Support:

Now I am using FPGA(XCKU3P) to receive sampling data from AFE58JD48 through JESD204B.

The AFE configuration is JESD 160X Mode, Subclass2, 16bit-30MHz sampling rate, which is configured by SPI according to the following process:

0x12 0x000A //PAGE_SEL_8CH_DIG1, PAGE_SEL_8CH_DIG2 = 1

0x31 0x00C0 //PLL_MODE = 160X, CTRL_K=1, CTRL_MODE = 1

0x32 0x8000 //EN_1L_MODE0 = 1

0x34 0x1107 //JESD_SUBCLASS = 2, JESD_VERSION = 1, K = 8

0x35 0x00C0 //L=1, CTRL_L = 1, CTRL_M = 1

0x36 0x0003 //M = 4

0x5D 0x8000 //EN_1L_MODE1 = 1

0x2C 0x0008 //EN_1L_MODE2 = 1

0x30 0x8002 //Enable Mux Pdn. Mux_Pdn_3_4; Bring Lane3 on Lane2; Pdn JESD2 (for Top ADC)

0x30 0x8006 //Mux_Pdn_5_6;Bring Lane5 on Lane8;Pdn JESD1(for Bottom ADC)

0x12 0x0000 //Disable Page Select

0x12 0x0002 //PAGE_SEL_8CH_DIG1 = 1, Selecting Top 8 channel

0x5F 0x00A0 //Pdn Lane 2

0x12 0x0008 //PAGE_SEL_8CH_DIG2 = 1, Selecting Bottom 8 channel

0x65 0x0050 //Pdn Lane 7

0x12 0x0000 //Disable Page Select

FPGA firmware Use Xilinx IP JESD204(7.2),1-Lanes,8-F,8-K,4.8Gbps-LineRate。

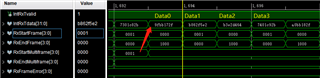

The Bit file is generated and downloaded to FPGA, and rx_data is obtained through ILA. I want to know how to convert rx_data into sampling data of each channel.