Hello,

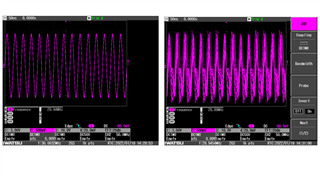

My customer uses DAC5688 on their own board. They sometimes get good waveform as shown lower left, but they sometimes don't do as shown lower right. Would you please tell me what do you suppose the root cause would be?

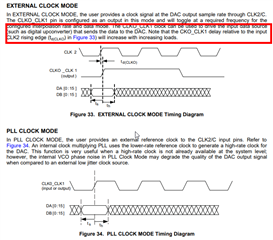

When they get the right one, it returns to normal only when they do hardware reset or PLL_sleep(CONFIG26 0x0d -> 0x0e -> 0x0d). I mean when they get good one, they can keep it unless they do hardware reset or PLL_sleep. When they get abnormal one, they can't make it to good one unless hardware reset or PLL_sleep.

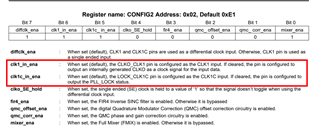

These are the register settings.

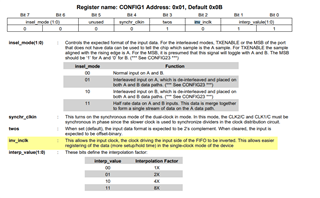

Addr. Data

0x04 0x00

0x05 0x80

0x06 0x00

0x07 0x00

0x08 0x00

0x09 0x00

0x0A 0x00

0x0B 0x00

0x0C 0x00

0x0D 0x00

0x0E 0x00

0x0F 0x24

0x10 0x00

0x11 0x00

0x12 0x00

0x13 0x00

0x14 0x00

0x15 0x00

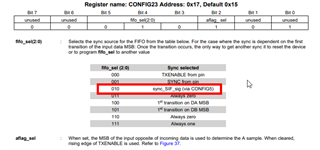

0x16 0x15

0x17 0x00

0x18 0x80

0x19 0x00

0x1A 0x0D

0x1B 0xFF

0x1C 0x00

0x1D 0x18

0x1E 0x13

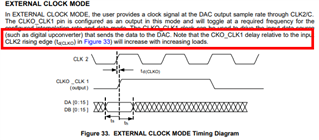

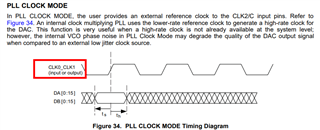

Note that they don't use complex mixer. Note also that they confirmed the recommended startup sequence shown on page 45, the timings(PLL clock mode) and clock input(CLK2/CLK2C) shown on page 7. Nothing seems wrong, but it sometimes doesn't work well. I'd like to know the reason why it is.

Best Regards,

Yoshikazu Kawasaki