Other Parts Discussed in Thread: ADS131A04EVM, ADS131A04, ADS131M04EVM

Hi team,

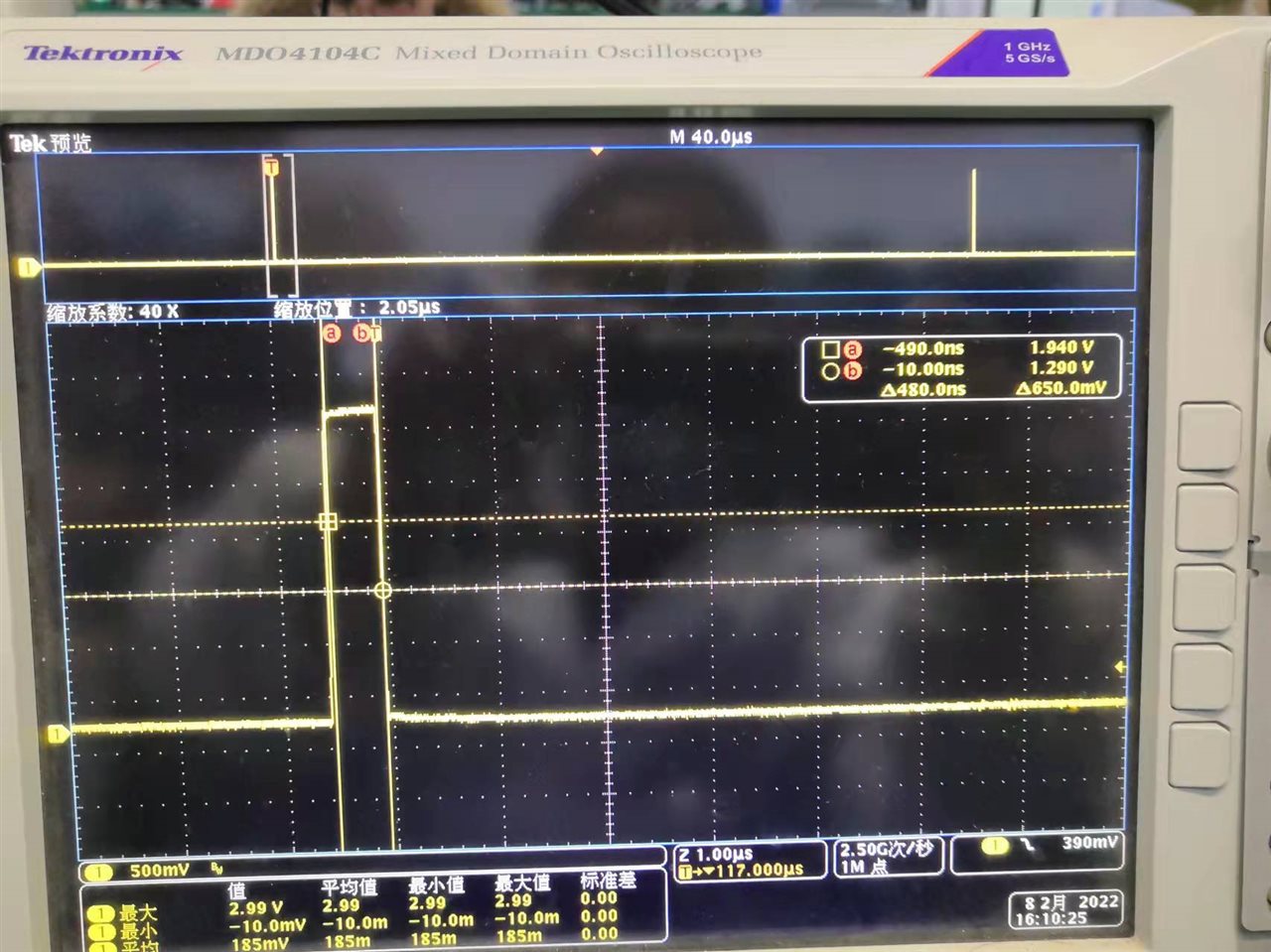

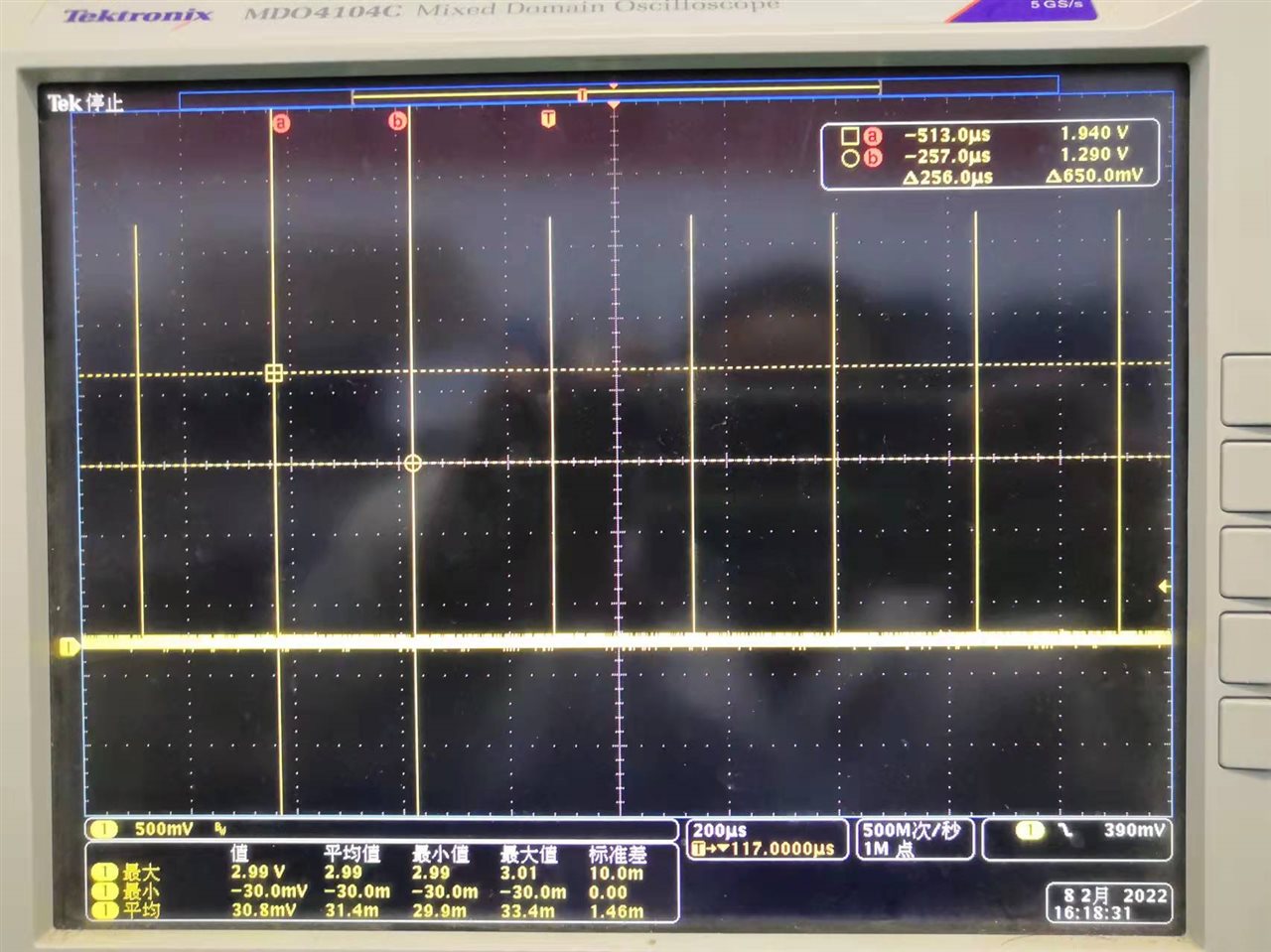

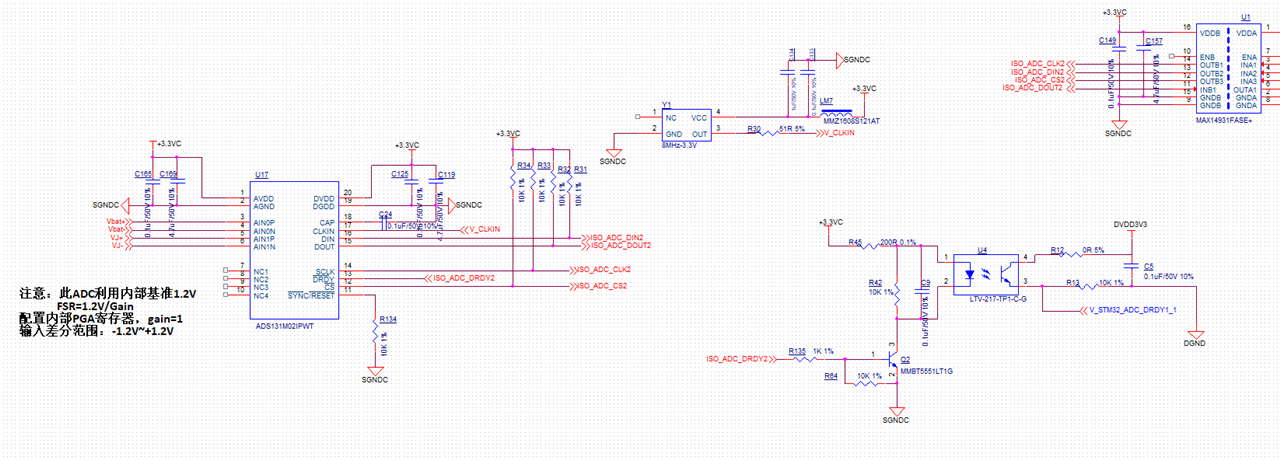

This is a new design in my customer. It is the first time for them to use ADS131M02IPW. They found DRDY output a periodic pulse with duration is about 480ns and cycle time is about 256us as below shows. What does it indicate? I would like to see if you have the same experience of that, then I will visit this customer to check more details.

Thanks.