Hello:

At present, we are using FPGA to access the internal register of ADC chip and read and write it. We need to consult you with the following questions:

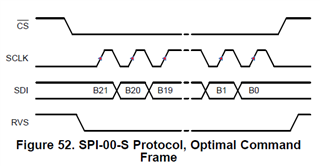

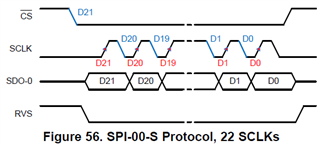

1、During the read operation, the host (FPGA) will first send the read instruction and wait for it to be sent, and then send an NOP instruction. While sending the NOP instruction, the host receives the data from the ADC chip. Is the above reading process correct?

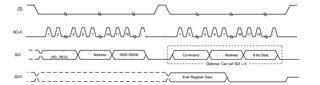

2、In combination with relevant timing requirements, the timing of SPI interface I designed is as follows,Is the design correct?

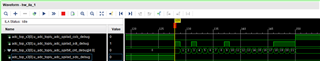

3、To access the data inside the ADC chip_ Take cntl register as an example, address = 010h, write its value as 0x0f, and send a write instruction: 0x24100f. The actual SPI interface timing is shown in the figure below:

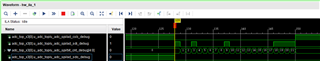

Read data for_ For the value in cntl register, first send the read instruction: 0x221000, and then send the NOP instruction: 0x000000 after the read instruction is sent. The actual SPI interface timing is shown in the figure below:

If the operation is correct, should the read value be 0x22100f? Is the timing design of the above interfaces correct?

4、If I want to read the data result after ADC chip conversion, I will first pull up the convst signal for 35ns, and then pull it down. After the RVs signal is pulled up, I start to send a NOP instruction and read out the converted data at the same time. Can you read the correct conversion data according to the above process?

I hope you take the time to have a look, thank you!

REF1: ADC chip model ads8924b.

Ref2: SPI timing protocol I use the power on default configuration spi-00 format, X1 mode, and the clock frequency is 40MHz. I send data on the falling edge of the clock and collect data on the rising edge.

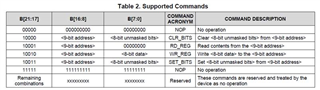

ReF3: the definition of ADC chip instruction format is shown in the following table: