Hi,

Greeting of the day!!

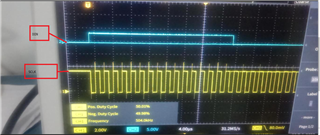

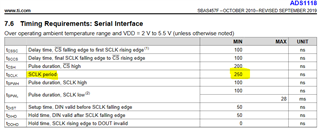

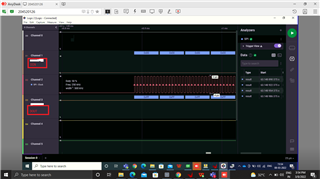

I am interfacing ads1118 with fgpa board( xc7a100t),with spi 3 wire mode(cs' permanently tied to gnd) and configuring registers with its default value .I am trying to read adc channel 0 with input given as 2.5v, but i am reading -1.DOUT pin is always high ,i have attached din ,sclk cro results. i have few questions

1.do i want to configure DOUT/DRDY' as interrupt pin at controller side?

2.what is minimum clock speed required for the device to work ?

3.Is 3 wire spi mode applicable to the device?

With regards

Ajay