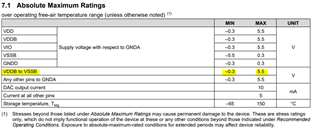

Hello. During evaluation of this device in my modules I continue to see the negative supply rail run away with excessive current and devices getting damaged, My eval boards have the VIO at 3.3V, VDD at +5V and VSSB at -5V. I have adjusted my test to sequence supplies properly but am still concerned that a turn-on event in my top level assembly can render the LMP92066 part useless because of damage. The damage usually happens if -5V is turned on first, without turning on the +5V or +3.3. This is probably something that should be getting more attention from TI.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.