I am facing noise problems with ADS1220.

I got placed ADS1220 ADC and a GSM module on the same multi-layer board. When GSM starts transmitting, measurements of ADS1220 starts being inflated.

For reducing amount of problems I am now analysing internal temperature measurements only, but problems are the same for temperature and analog inputs.

Temperature measurements are taken 20 SPS, normal operating mode, continuous conversion, temperature sensor enabled, internal 2.048-V reference, simultaneous 50-Hz and 60-Hz rejection. DRDY pin is checked before reading.

When GSM transmits and antenna is moved by user towards the module (depends on location and surrounding environment), temperature measurements are being increased about 4oC for the entire time of transmission.

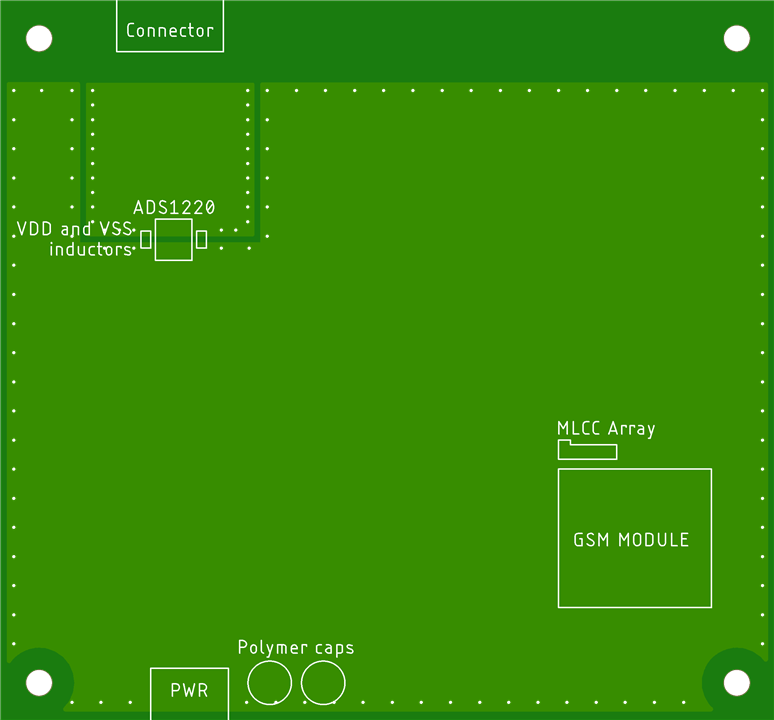

DVDD and AVDD are decoupled with 0.22uF capacitors. DVDD/AVDD and DGND/AVSS are connected through 0.1uH 0805 inductors. CLK connected to DGND and AIN3 is floating. AIN0/1 have anti-aliasing RC filter 47uF - 200Ohm and decoupled from GSM noises with capacitors 10pF/33pF/2.2nF. Power itself is tightly decoupled near to the GSM module and when GSM antenna is placed opposite direction there is no noise, so it is not a general powering problem. If I connect AIN0 and AIN1 pins tight, noises are still present so it is not a noise inducted outside.

It looks that noises are inducted internally inside the ADS1220 (package TSSOP16). What can I do more for reducing the noise?

When I measure the voltage on AVDD-AVSS (every time, not only when GSM transmits) I observe voltage spikes every 2us that are not present on DVDD/DGND. Is it expected?

Example readings (one reading/line per 200ms):

Value converted to oC Value read

23.156250 741

23.156250 741

23.156250 741

23.156250 741

23.156250 741

23.156250 741

23.156250 741

23.187500 742

23.187500 742

23.500000 752

23.156250 741

23.156250 741

23.187500 742

23.187500 742

23.187500 742

23.500000 752

23.968750 767

23.968750 767

25.218750 807

25.375000 812

27.250000 872

27.062500 866

27.250000 872

27.468750 879

27.250000 872

27.281250 873

27.250000 872

27.250000 872

27.062500 866

26.875000 860

23.718750 759

23.625000 756

23.656250 757

23.625000 756

23.718750 759

23.656250 757

23.562500 754

23.500000 752

23.218750 743

23.218750 743

23.218750 743

23.187500 742

23.218750 743

23.187500 742

23.187500 742

23.187500 742