Other Parts Discussed in Thread: ADC12DJ3200

I was finally able to get a simulation working when i use the Xilinx JESD core, however when i try my design in the hardware it doesn't work.

One possible issue is the fact that the ADC12J3200EVM has 4 JESD channels that are reversed. On the FPGA version that was shipped with the example project (https://www.ti.com/technical-documents/mytilit/export-control?litId=SLVC698&fileType=zip&&ts=1650494201216), there is this note

ADC12DJ3200 RevA EVM is used for testing. In this EVM revision P & N pins of upper four SERDES lanes are swapped, hence Rx lane polarity inversion is implemented in the design to address that. Due to this, Rx lane polarity inversion constant given to the PHY module is 240.

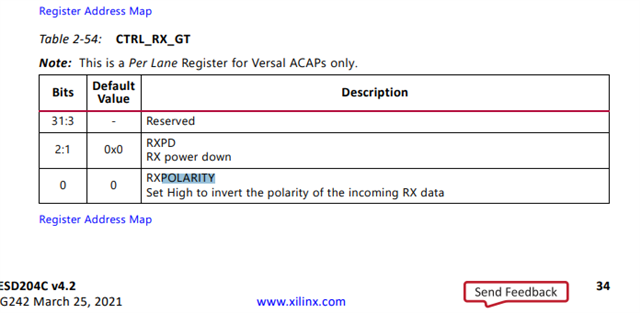

In the 2020.2 version of the xilinx tools it appears that the rxpolarity input to the JESDPHY no longer exists and i don't see a register that is not "Versal ACAPs" only that has polairty setting (Here's the product guide Xilinx's JESD core for https://docs.xilinx.com/v/u/en-US/pg242-jesd204c )

So my question is, how can i get the polarity pins reversed for the last 4 channels.