Other Parts Discussed in Thread: ADC3662,

Dear Ladies and Gentlemen,

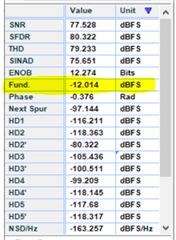

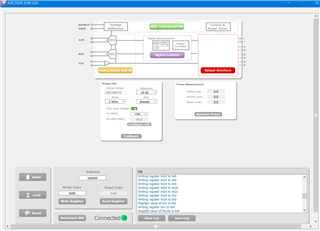

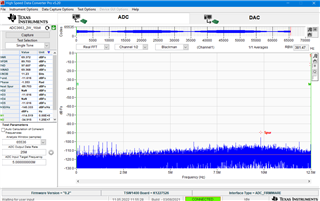

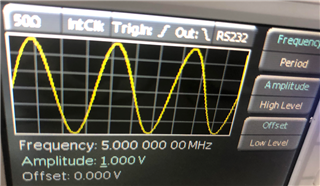

We have recently acquired an ADC3662EVM and a TSW1400EVM. We have tried to put the device into operation with the help of the userguide. We use the internal clock instead of an external clock. The hardware modifications were made as described. Now we wanted to connect an external signal to the adc as described, but we are not quite sure how many volts the input signal may have maximum. Since the user guide only describes that the signal should have ( 5 MHz at a power level of ~ +15 dBm), but we have to set the amplitude power level and offset on our signal generator, we looked for the internal resistance of the analogue input in the data sheet of the ADC to calculate the max voltage. But we were not quite sure what the internal resistancee of the ADC3662 is and how high the maximum voltage of the signal may be.

Many thanks in advance.

Kind regards

Quirin