Hi Teams,

I'm evaluating DAC38J84 according to SLAA696 DAC38J84 device initialization and sysref configuration. However, I came across several problems. Can you help me to solve these issues?

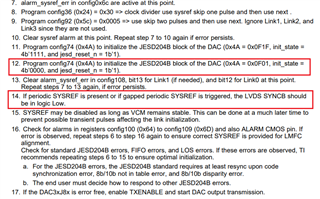

1, SYNCB will be pulled low, after step 12. This results into the reconnecting of communication. FPGA will continuously send the reconnect request.

2, Can you help to explain the step 14 to me, I don't understand this step.

Thanks and BRs.

Marsh