Hi team,

How much is the digital input threshold voltage?

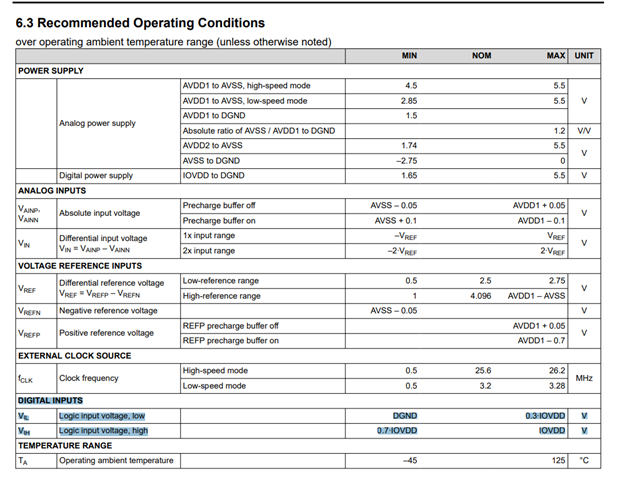

I can only see the data below in the datasheet.

What will the logic become when input 0.3*IOVDD~0.7*IOVDD?

Best regards,

Yuto

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

How much is the digital input threshold voltage?

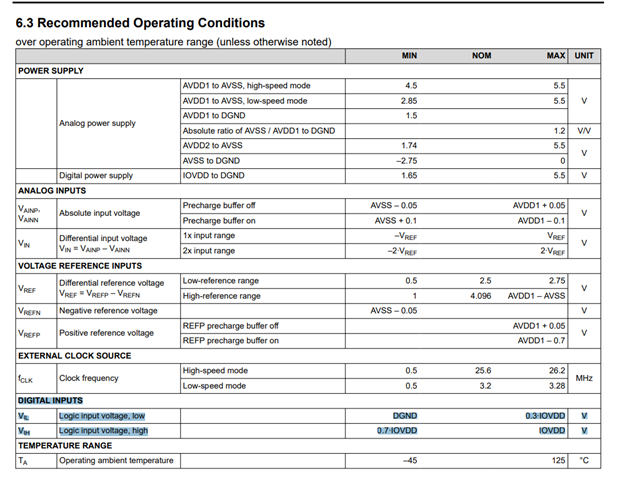

I can only see the data below in the datasheet.

What will the logic become when input 0.3*IOVDD~0.7*IOVDD?

Best regards,

Yuto

Hi Yuto,

The digital input thresholds are defined by your IOVDD supply voltage. For example if IOVDD is 5V then your input LOW threshold (VIL) will be a maximum of 0.3 * IOVDD = 1.5V and your input HIGH threshold (VIH) will be a minimum of 0.7 * IOVDD = 3.5V.

This means that you need to ensure your digital inputs will be provided a signal that is 1.5V or below to indicate a Logic LOW and 3.5V or above for a Logic HIGH for an IOVDD = 5V. Otherwise, you will be in a undefined logic state where the logic level can be either HIGH or LOW.

Anyone from the ADC team, feel free to correct me if I am wrong. Thanks!

Cheers,

Fadi