Other Parts Discussed in Thread: ADS1299, ADS1298R

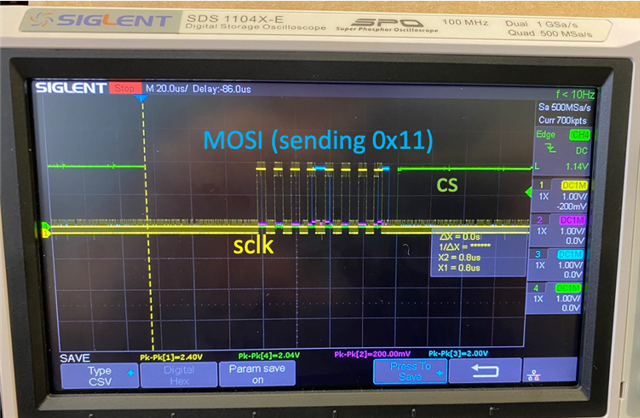

I tried to build interface with ADS1299 through SPI.

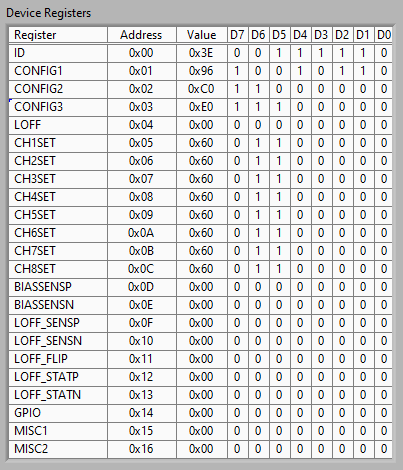

The SPI is not working and the it kept reading 0x00 from ADS1299.

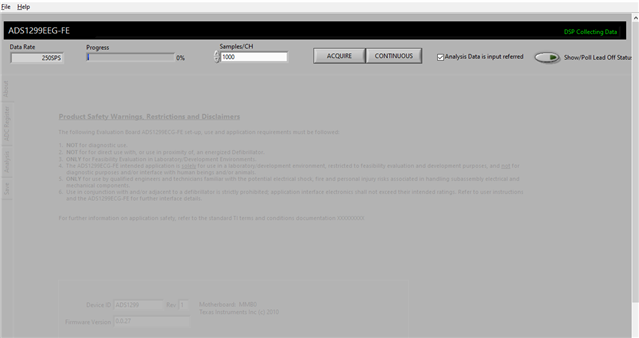

My assumption is that the ADS1299 is not working. So I tried to read the data from the software on PC through UART.

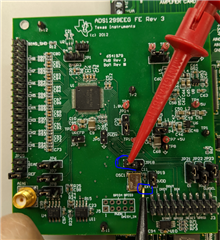

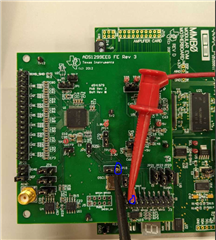

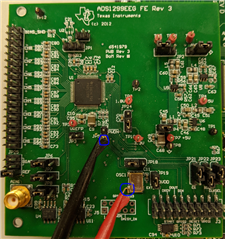

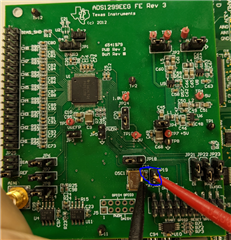

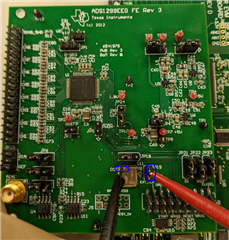

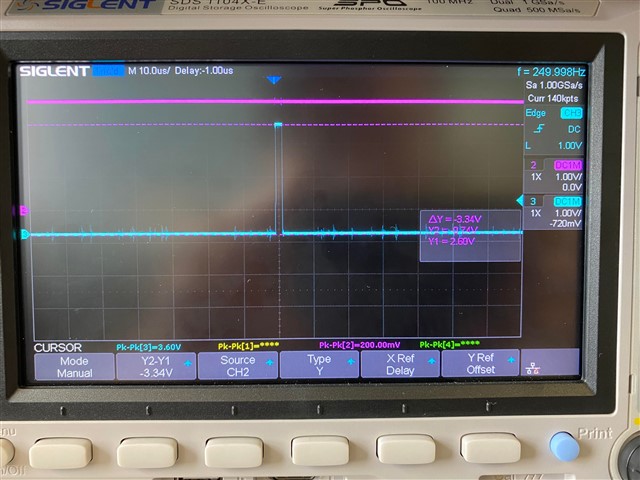

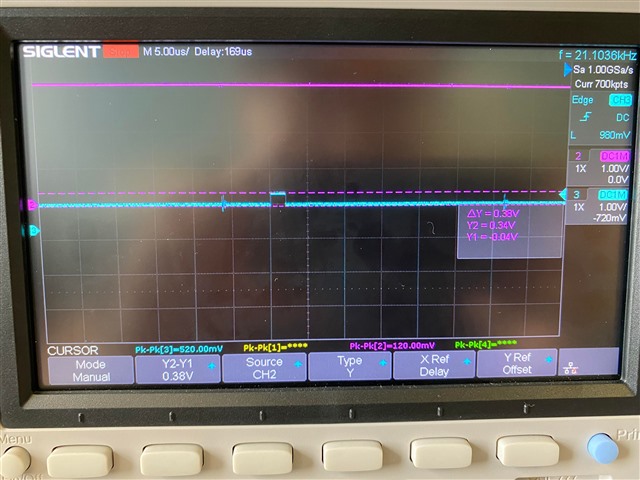

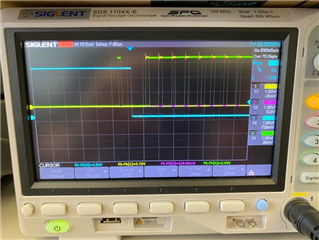

Then it stuck at the reading register step, the data rate is 16000SPS and took over than 15 minutes. After this was done, the software shows no responding whenever I clicked any button on the GUI interface. I found that the seven segment light on MM0 looks like this (picture attached).

These are what I have tried (MM0 is only connected to PC. The SPI wiring and channel input are all disconnected) :

1. press the reset button on MM0.

2. remove the power jack and connected it again.

3. remove the usb to PC and connected it again.

4. reinstall the software.

5. change the connect PC.

All of above didn't solve the problem. I think this issue is similar to https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/412720/ads1298recgf-fe-stuck-at-reading-registers?ADS1298RECGF-FE-stuck-at-reading-registers. But this thread ended up just got a new board.

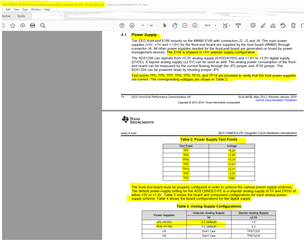

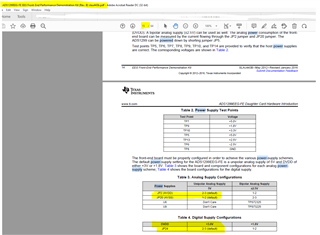

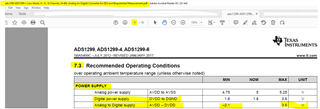

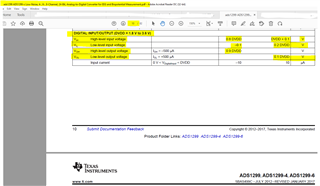

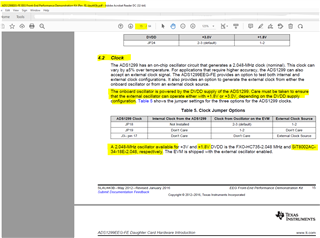

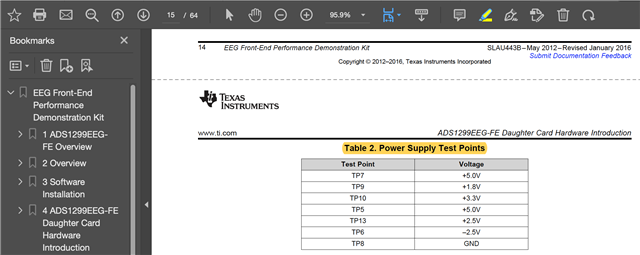

Also, I didn't change any hardware setting except that the VDDD is connected to 1.8V.

Could you provide some suggestions on what might cause the issue?

Thanks!