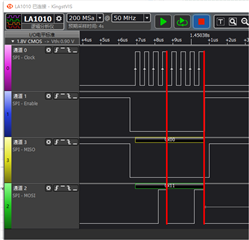

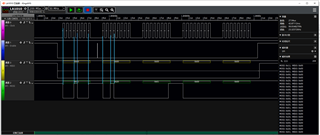

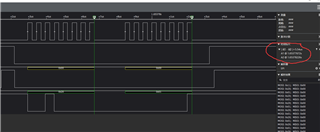

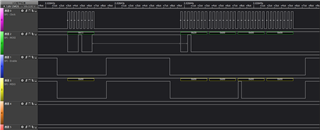

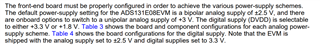

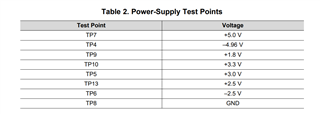

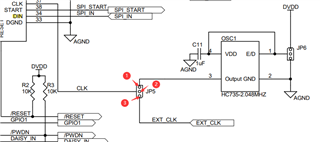

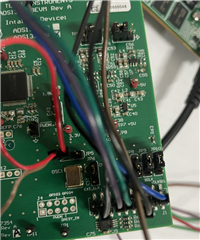

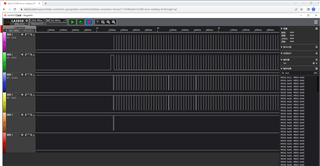

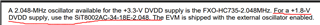

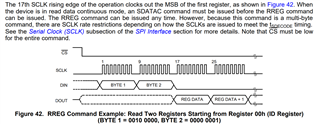

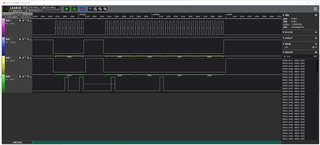

According to the instructions of the datasheet, I send the SDATAC instruction first, then delay 2μs (frequency is 2MHz), then send 0x20 0x01 (ID register address is 00h), resulting in the following waveform.

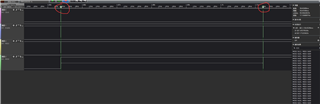

It seems that after I send the data, ADS131E08 does not have any response, I would like to ask what might be the problem?