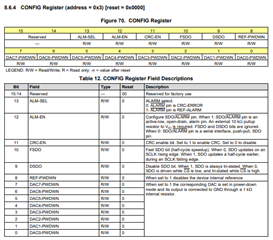

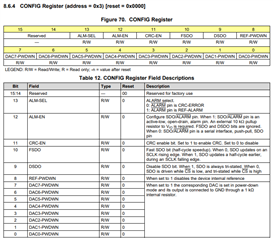

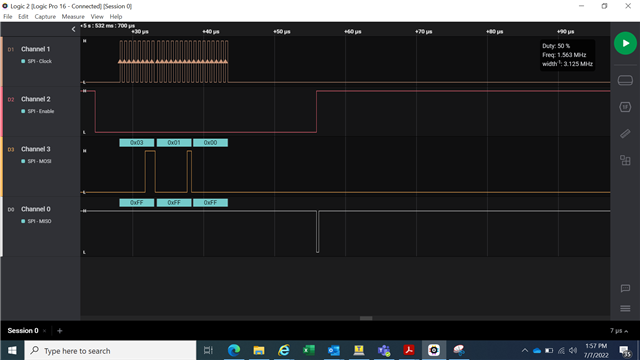

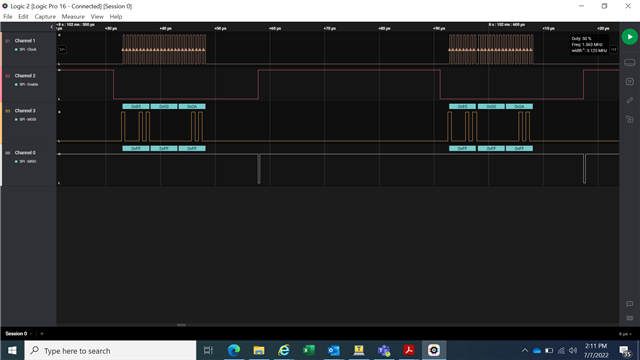

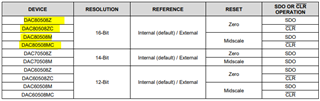

Value read from DAC80508 via SPI is always 0xFF.

Observation:

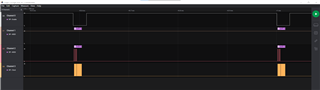

MOSI: correct output is observed on pin 15(SDI) of DAC80508.

MISO: output observed is always 0xFF on pin 14(SDO) of DAC80508.

SCLK: Clock is observed.

nCS: Chip select is observed.

Voltage level:

Pin 1(REF): Between 2 & 3 volts

Pin 16(VIO): Between 3 & 4 Volts.

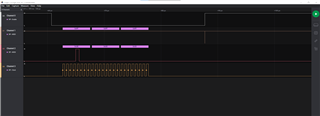

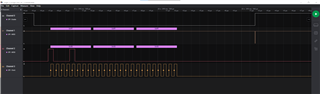

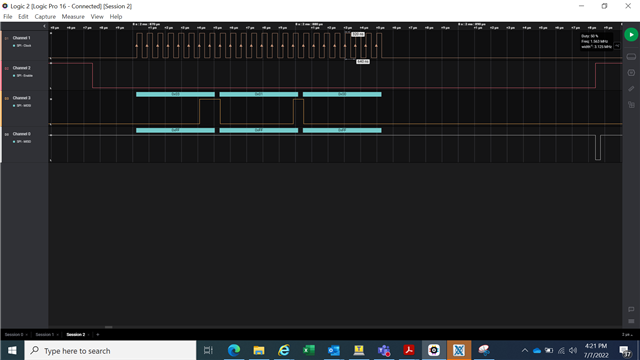

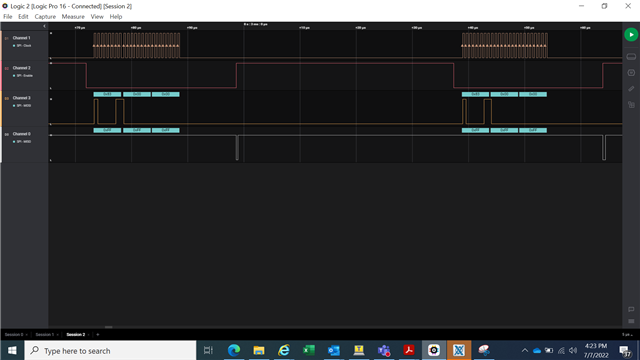

Attaching data captured on logic analyzer Saleae.