Hi Team,

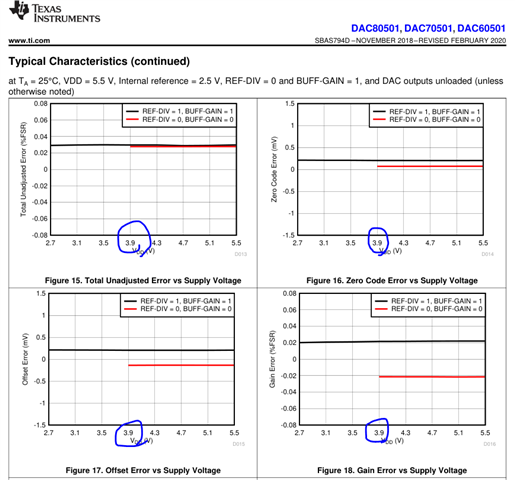

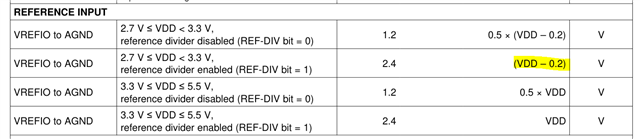

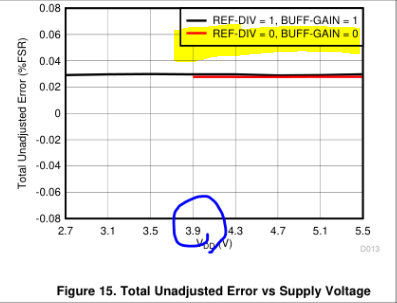

I have a question on the figures in datasheet. As captured below, the data indicates only down to VDD=3.9V when REF-DIV=0 and BUFF-GAIN=0. Could you explain why the minimum supply 3.9V comes into play here?

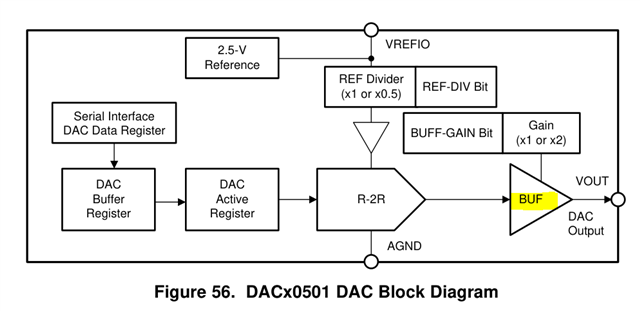

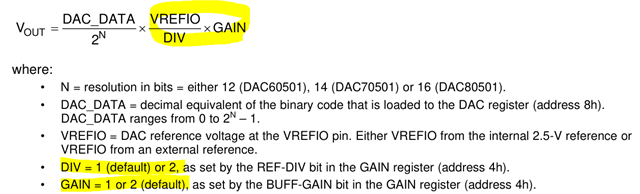

Basically, this question arises while I try to figure out how two registers should be set for the best accuracy because REF-DIV=1 and BUFF-GAIN=0 would result in same result with REF-DIV=0 and BUFF-GAIN=1.