Hello Team,

can you clarify the following points:

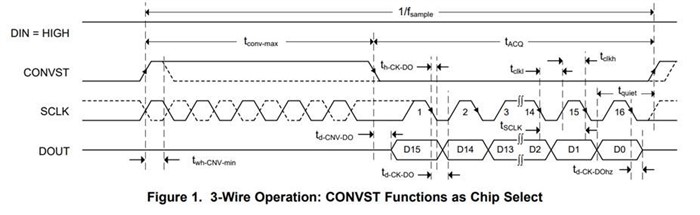

- Tsample is defined by tconv_max and tacq. Tconv_max is 1300ns so that 1200ns are left for tacq (which is at the same time the minimum for tacq) to reach 2500ns tsample (400kSps).

- tacq = 1200ns = td_cnv_do + 16 tsclk + margin -> tacq = 12,3ns + 16x62,5ns + margin @ 16MHz SPI SCLK

- -> meaning that with a SPI SCLK of 16MHz the timing constraints are reachable for 400kSps if you prolong tacq to 1200ns

- Is that correct?

- tacq = 1200ns = td_cnv_do + 16 tsclk + margin -> tacq = 12,3ns + 16x62,5ns + margin @ 16MHz SPI SCLK

- As long as DIN and CONVST are high other ICs on the SPI bus can use SCLK and DOUT without any conflicts, right? So the ADS8864 doesn’t react on any SCLKs and leaves DOUT on high impedance during that time? So I could communicate with other ICs while DIN and CONVST are high.

- DOUT becomes high impedance after the 16th SCLK → meaning that CONVST can be left low until the next conversion cycle and other ICs can use SCLK and DOUT in the meantime without any conflicts?

Thanks,

SunSet