Hi Experts,

Seeking your assistance on this query posting on behalf of my Cx:

SETUP:

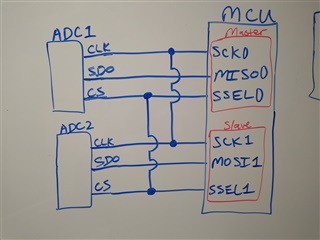

I have two analog-to-digital converters (both ADS7044IDCUR) setup for acquisition of a static, DC signal and communicating with a microcontroller. I am trying to retrieve data from both ADCs simultaneously. To do this, I have one SPI bus on the microcontroller configured in master mode and the other SPI bus configured in slave mode. I then have the master's slave select and clock tied to the slave's slave select and clock. In this way, the master can clock data from one ADC into its own RX FIFO and from the other ADC into the slave's RX FIFO simultaneously.

PROBLEM:

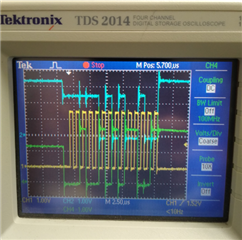

The slave's ADC is clocking out accurate data/values as expected. However, the problem I am encountering is that the master's ADC is not clocking out proper data. By this I am primarily referring to two issues. First, the master's ADC is clocking out data that is very random and inconsistent (there is no noticeable pattern or general proximity of values). Some values even have bits 12 and 13 set to 1, which is impossible according to the datasheet. Second, the digital signal on the SDO pin of the master's ADC is malfunctioning, being caught in an intermediary voltage level between high and low at times. I have attached a picture from an oscilloscope to illustrate this. In the image, the yellow signal is the clock, the blue signal is the master's SDO from its ADC, and the green signal is the slave's SDO from its ADC. As you can see from the image, the master's SDO high signal is clipped below a true 3.3V high signal, while the slave's SDO high signal reaches a true 3.3V high signal.

Do you have any idea why the master ADC would be behaving in this way?

I have verified that none of the master ADC pins are shorted together, and that the supply voltage rails for both master and slave ADCs are as expected. My clocking frequency is ~1MHz.

Thank you.

Regards,

Archie A.