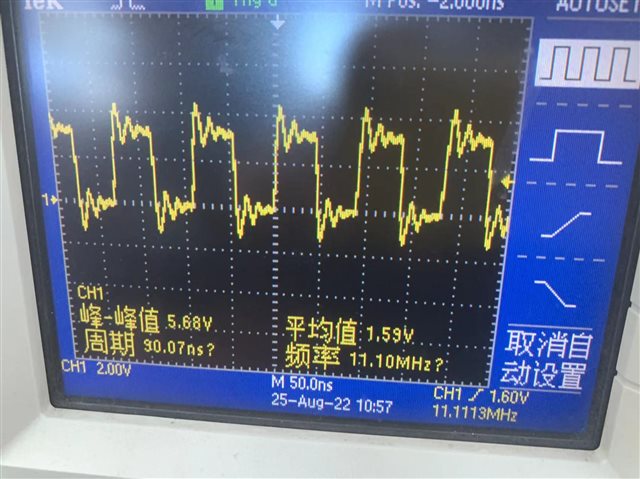

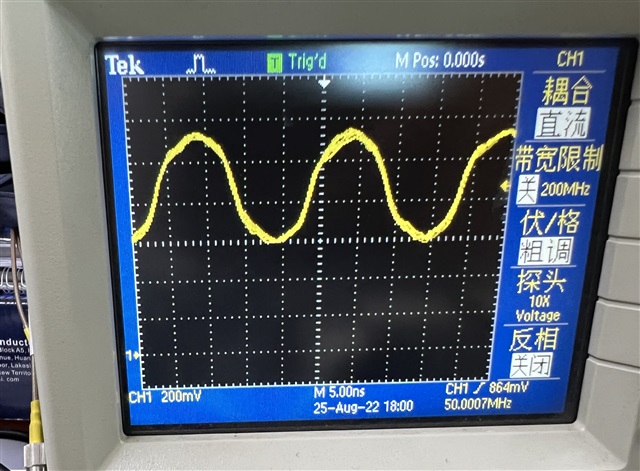

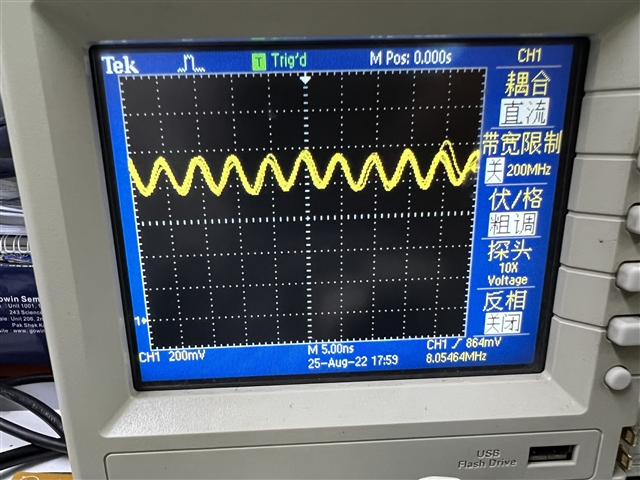

Hello, I am using ADC3663 and the settings are as follows when sampling at 50MHz: 2wire, 16bits, and DDC set to bypass, CLK input clock is 50MHz, and DCLK input clock is 200MHz. However, the FCLK clock output by AD is not 25MHz and its duty cycle is not 50%. Then other sampling rate tests are performed as long as DDC uses bypass, It is found that the FCLK output of AD is not a clock signal with a duty cycle of 50%, while the extraction rate of DDC is set to 2 or other normal. May I ask what register setting error may cause this phenomenon?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.