Other Parts Discussed in Thread: AFE5832LP

Hi,

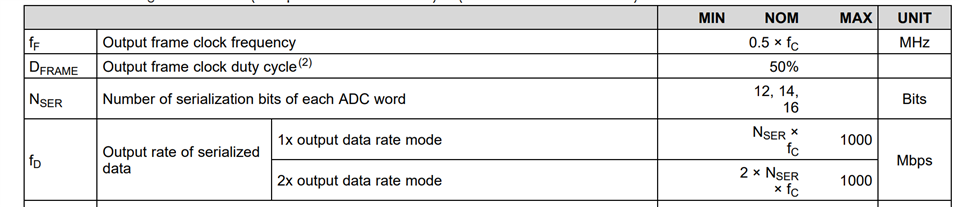

I bought AFE5832Lp from TI. I have a problem reading the AFE5832LP data sheet. 1- It mention that the fc = 80 MSPS (sample rate = 40 MSPS). Which one is the date rate? Because if I consider date rate = 40 MSPS the bit clock and frame clock will be 40 MSPS and 400 MSPS and serialized data rate of 800 MHZ for 10-bit resolution. 2- Since AFE5832LP has 16 ADC for 32 channels, should I divide by 2 each of the above-mentioned clock values? 3- What is the reference frequency of it? I am very confused about reading the data sheet. Can you please help me with my question? I would appreciate it if you could please fill in the blank for me below.

The AFE5832LP board consists of 32channels, 16 ADCs with 10 bits resolution, and ....? The bit clock is aligned with the center of the data. Well, I have a frame clock frequency of ....?, a bit clock of .....?, and a data rate o .....?

Thanks,

Ruzb