Other Parts Discussed in Thread: ADS4128, ADS4149

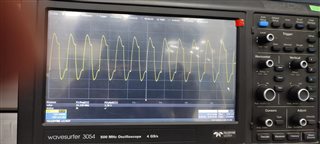

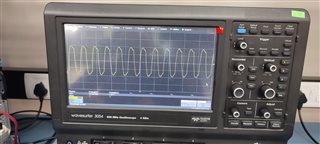

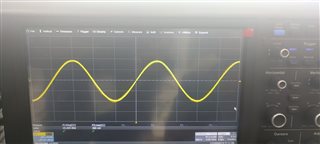

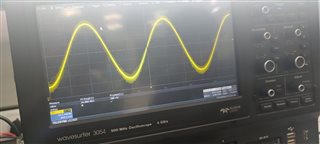

In our custom board we are using ads4129. the register configurations are x"41C0", x"3D80",x"4208", x"DF30", x"0303", x"4A01", x"2503", x"2500". the sampling clock is 24Mhz. we have captured the data on fpga and analyzed in matlab. after aliasing the expected output frequency is not coming. We ensured that the fpga captured output and the adc output(we probed and checked the msb bit of the adc output pins) are matching exactly, so there is no fault. then what might be the reason for this issue? for the reference I have attached the input clk,output_clk, and input fft output for the input frequency.