Hello,

As stated in the title, I am getting unexpected behavior at the DRDY and SDO pins. This is what I do before starting conversion:

1. Reset ADC & configure 3-wire SPI mode (CS held low during reset procedure)

2. Write b10000000 to CONFIG4 register (external ADC clock)

3. Read CONFIG4 (response: b1000000) and STATUS (reponse: b1100000) registers.

The ADC clock is externally set via my STM32 uC to 25.6 MHz (0.1% error) which should result in a sampling rate of 400 ksps (as shown by the reponse of the DRDY pin). I understand that I get a AVDD1 undervoltage warning (STATUS register) but it is set precisely to 4.5 Volts, which I think is still within the recommended operating conditions (datasheet page 5). CS is always held low after starting my conversions (START pin set high).

I am actually running two ADCs in parallel with START, CLK, SCLK shared for fully synchronous operation. The STM32 generates the SCLK signal on a separate pin which is connected to the SCLK pins of the two SPI peripherals. Both SPIs are configured in Full-Duplex Slave mode.

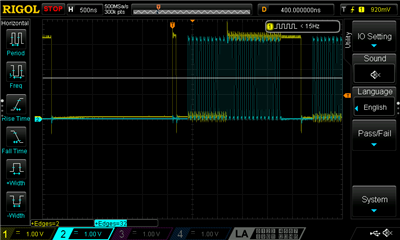

I essentially get no data output and DRDY does not go high when sending the SCLK pulses (which it should do after 8), except after the first conversion cycle where weird stuff happens. Here is the oscilloscope output:

Any help is greatly appreciated!

-- Dan