Other Parts Discussed in Thread: ADS4122,

Hi,

I will using LVDS clock driver to drive the clock input of the ADS5296A and ADS4122.

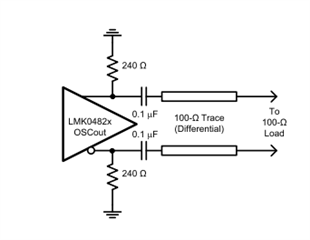

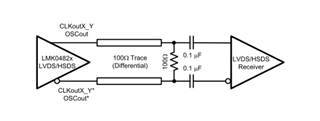

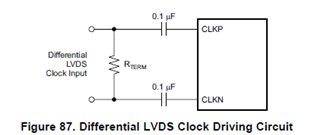

in the DS of ADS5296A I find the followed:

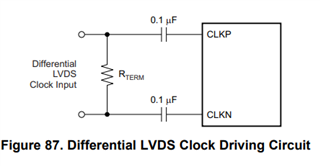

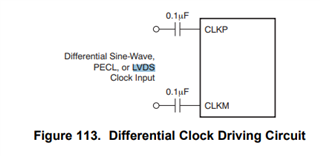

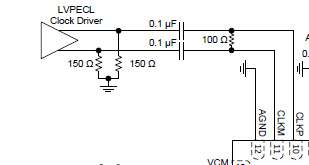

The answer to the same question for the ADS4122:

Pls. advise where to put the termination in both cases.

regards

Zeev Gerber