Hi Team,

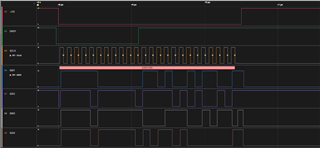

I have a board with 4x ADS127L11s in parallel. They all share the same SDI line, hence they should all be configured the exact same. However, one of the ADS127L11s (SDI2) that I'm reading conversion data from stays high after all the data has been shifted out. None of the other three ADC do this. Do you know why this may be?

They were configured to be in data output and DRDY mode, so they should all be behaving like SDI2. Thank you in advance!