Other Parts Discussed in Thread: ADS8900B

Hi Team,

Can you please help us with this inquiry of our customer.

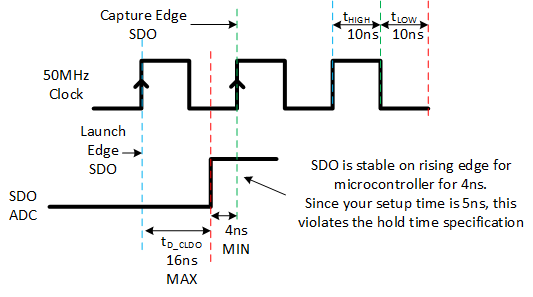

From the datasheet, the D_CKCS: SCLK launch edge to (next) data is valid on SDO. What is the launch edge, leading or trailing edge? The CPHA and CPOL are 0.

We run ADS7066 SPI at 50MHz and want to understand the SDO timing to confirm that it is "clocked out" by the SCLK trailing edge.

The tD_CKDO MAX = 16 nS is making problems in our design.

What is the tD_CKDO MIN? The MAX exceeds the half SCLK cycle that makes it misses the following SCLK leading edge. The SPI Master device has the Master (MOSI) input setup = 5 nS min

Regard,

Danilo