Hello team,

My customer requested the additional specification which is not stated in datasheet.

Can you provide below information?

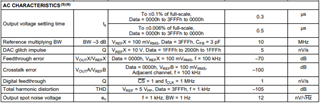

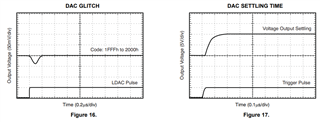

- 10% to 90% settling time (input, output)

- digital delay (= interface delay)

- Spurious free dynamic range(SFDR)

- Intermodulation distortion

Thanks.

Best Regards,

Austin