Other Parts Discussed in Thread: ADS1263

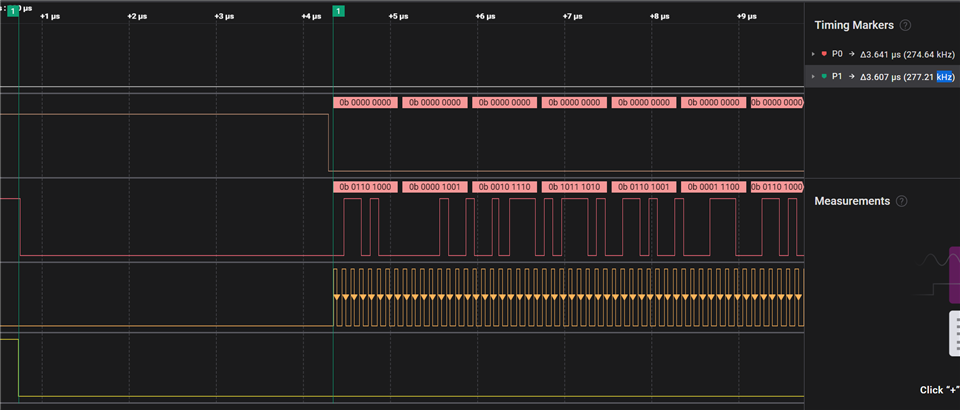

I have an ads1262 with the following setup

reading differential input on ain0 and ain1 every 10

400sps

gain 16

CRC and status byte enabled

1 out of about every 12000 reads (about every 2 minutes) I get a reading where the bits are all shifted left 1. This is very odd and will still pass the CRC test, along with messing up my system because of the bad read being double what the last one was.

The above image is the read right before a bad read. (top to bottom MOSI, MISO, CLK, CS)

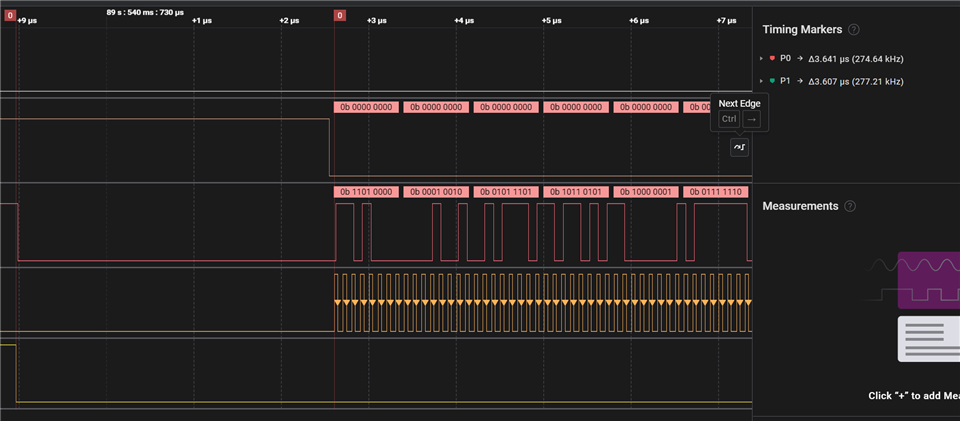

This image reading is roughly 10 ms after the reading above it. As you can see all of the bits are shifted over to the left one. I am able now to use the Status bit to show that it's a bad read since I don't have an ads1263 the 8th bit should always be 0, also I'm using an external clock so the 6th bit should be 1. I've found how to hopefully not let this affect my system. I'm curious is this a common problem(it happens on the 6 prototype boards I have) What can I do to fix this? It happens at all clock frequencies, it is much more prevalent at lower speeds 1 MHz. Currently, I run at 10 MHz. My signals look very clean so I'm looking for some advice.