Good afternoon,

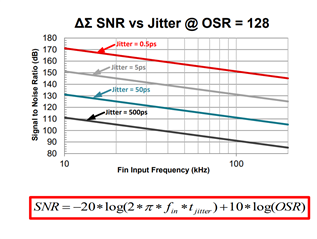

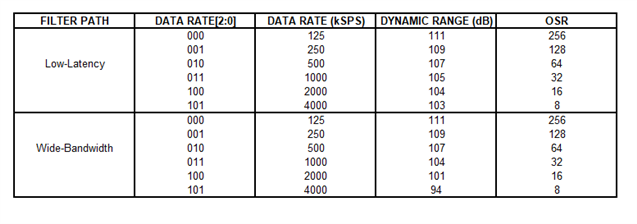

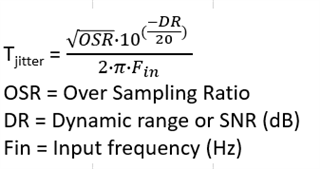

We're looking at using the ADS1675 for our design but could not find a specification in the datasheet that shows the relationship between clock jitter tolerance and SNR. Are there additional resources that show this correlation (graph or specifications)?

Thanks for the help!